IK3OIL are un site foarte interesant si binecunoscut printre colegii radioamatori. Unul dintre montajele sale cele mai utile este stabilizatorul de frecvente FLL realizat in jurul unui microcontroller PIC16F628. Documentatia originala poate fi gasita pe site-ul autorului si este in format PDF. Va asigur ca daca e realizat corect, montajul functioneaza din start. In ciuda faptului ca documentatia e clara si succinta, reusita punerii la punct a montajului depinde de un aspect foarte important care nu a fost descris in articolul original.

Probabil ca o parte dintre cei care au reprodus montajul nu l-au putut exploata corect tocmai datorita lipsei informatiilor necesare otinerii unui reglaj corect (ma refer la incepatori, in general). Tinand cont de intrebarea unui utilizator de pe forum, tintind exact spre aceste probleme, am postat pe data de 3 Sept. 2012 un raspuns pe care doresc sa-l reproduc in continuare, pentru o mai buna raspandire a solutiei respective printre pasionatii care doresc sa se bucure de buna functionare a montajului.

[ prima publicare: 3 Sept. 2012, aria CQ-YO @ Forumul Electronistilor (ElForum.ro) ]

Utilizatorul cyclonb a expus situatia de mai jos, punand urmatoarea intrebare (29.08.2012):

|

Inteleg ca la iesirea filtrului de netezire, ar trebui sa existe o tensiune care sa varieze in functie de frecventa de la intrare, sau gresesc? As dori sa va rog sa-mi spuneti si mie, daca se poate, ce tensiune (cc) puteti masura la iesirea respectiva, cu montajul in gol (fara a fi legat la diodele varicap ale placutei VFO) si daca aceasta variaza cand schimbati frecventa VFO-ului. Daca da, cam intre ce limite? |

Tinand cont de faptul ca in urma cu un an, reprodusesem si eu montajul dar nu il folosisem, am hotarat sa-l studiez mai atent, pentru a controla cu el VFO-ul receptorului sincrodina descris in articolul "POLAR3A: Receptor sincrodina pentru benzile de 80m si 40m", pe care l-am construit si de a carui functionare sunt foarte incantat.

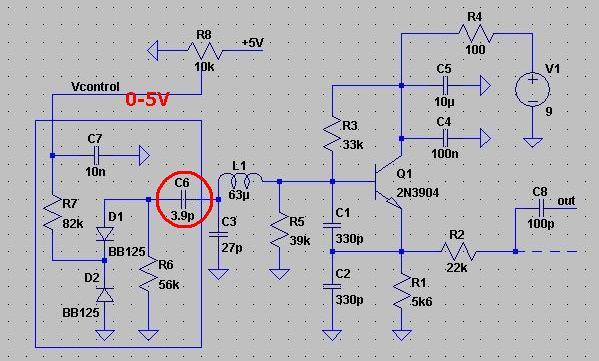

Schema VFO-ului este urmatoarea:

Circuitul de control prin diode varicap este cel descris de IK3OIL in montajul sau original, cu singura diferenta ca am fost nevoit sa micsorez valorea lui C6 la 3.9pF. Veti vedea in continuare de ce.

"Secretul" reglajului corect este amintit in PDF-ul oferit de autor, dar pasii necesari nu sunt documentati suficient. Daca e respectat, circuitul va da rezultatele mentionate. Pe scurt, excursia oferita de sistemul cu diode varicap trebuie sa nu fie mai mare de 15KHz, pentru o tensiune de control aplicata cu valori intre 0 si +5V. Pentru a realiza aceasta conditie, autorul trece in revista pasii necesari la finalul documentatiei, dar eu voi preciza modalitatea de reglaj impusa de conditiile de pe masa mea de lucru.

Mai concret, folosind un potentiometru (R8 = 10K, figurat in schema oscilatorului de mai sus) conectat intre masa (GND), +5V (preluati de la stabilizatorul PIC-ului) si pinul {Vcontrol}, se variaza cursorul acestuia intre cele doua extreme, notand excursia de frecventa. Aceasta trebuie sa fie de aprox. 15KHz, fara a depasi aceasta valoare. Cu C6 = 22pF, am obtinut o excursie de 52.3 KHz, iar cu 4.7pF, una de 17.69 KHz. Micsorand C6 la 3.9pF, excursia de frecventa s-a diminuat la 14.72 KHz.

Am demontat apoi potentiometrul si am conectat iesirea filtrului RC din placa de control, la pinul {Vcontrol} al diodelor varicap, folosind un cablu ecranat din coaxial subtire. Rezultatul nu s-a lasat asteptat, sistemul a facut LOCK, stabilizand alunecarea VFO-ului.

De notat ca initial, n-aveam de unde sti exact cum actioneaza circuitul de corectie si cum evolueaza tensiunea la iesirea filtrului din placa de control. Pentru a vedea acest lucru, am conectat un generator DDS la intrarea lui T2, inlocuind VFO-ul. Am fixat o frecventa in banda de 80m si apoi am verificat forma semnalului in colectorul lui T1:

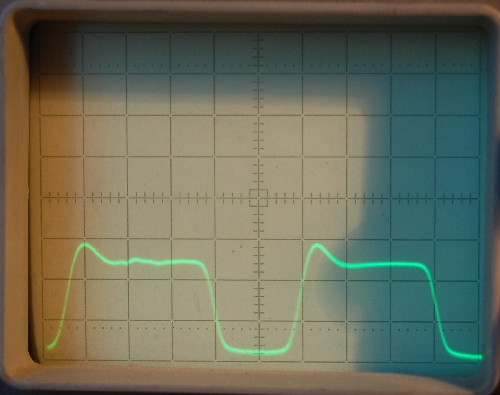

Circuitul format din T2 si T1 are rolul de a aduce semnalul sinusoidal de la intrare, la o forma apropiata de dreptunghi, necesara intrarii de la microcontroller. In colectorul lui T1 trebuie sa se regaseasca o tensiune apropiata de 1/2 din tensiunea de alimentare. IK3OIL a mentionat aprox. 1.8V, eu am masurat 2.33V.

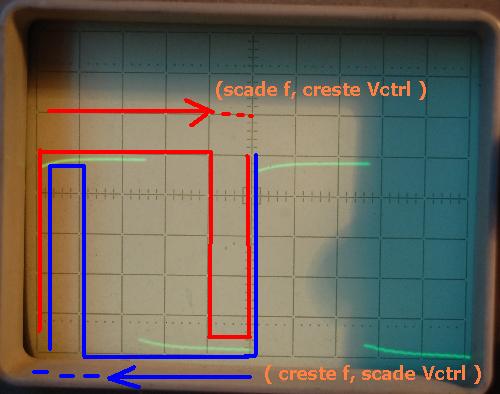

In primele 30sec. dupa pornirea montajului, atat timp cat acesta nu face LOCK, la iesirea filtrului de pe placa de control (Vc out), trebuie sa se regaseasca o tensiune continua foarte apropiata de jumatate din tensiunea de alimentare, adica in jur de 2.5V. Eu am masurat 2.53V. Dupa ce a facut LOCK, semnalul de la pinul 9 al microcontroller-ului va avea in prima etapa, un factor de umplere de 1/2, ca in poza de mai jos (trasa verde deschis, ptr. ca celelalte reprezinta tendintele in functie de evolutia frecventei):

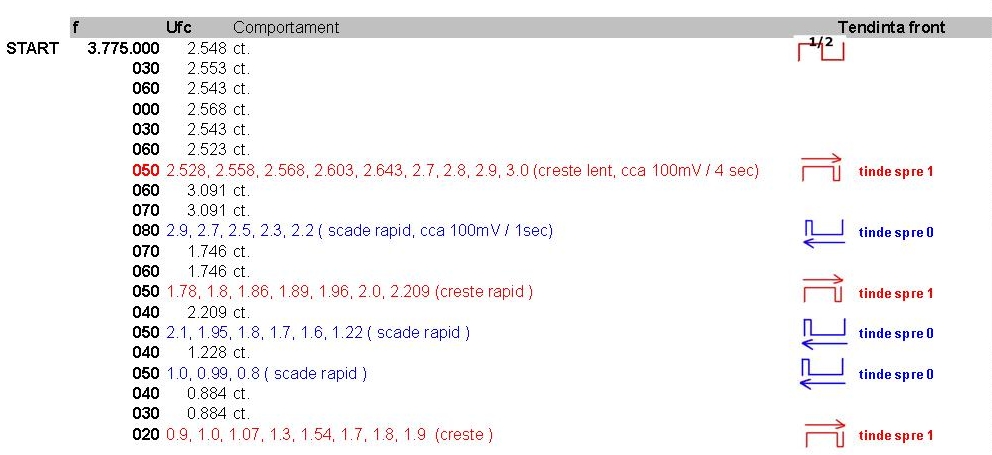

Pentru a observa variatia tensiunii de la iesirea {Vc out}, am conectat la acest pin un multimetru digital si am inceput sa variez frecventa generatorului, in sus si in jos, notand intr-un tabel valorea acesteia, valorea tensiunii rezultante pe {Vc out} si aspectul fronturilor PWM de la pinul 9:

Se poate observa clar ca atunci cand frecventa creste, tensiunea de la {Vc out} scade, semnalul PWM modificandu-si factorul de umplere (tinzand spre "0" logic). Invers, cand frecventa scade, tensiunea de la iesirea {Vc out} va creste, iar semnalul PWM isi va modifica factorul de umplere tinzand spre "1" logic.

Procesul este lent, iar pentru variatii mici de frecventa, nu se poate vedea pe osciloscop, ci numai pe AVO digital. In fine, in cazul in care excursia de frecventa oferita de diodele varicap depaseste 15KHz, softul din microcontroller va considera ca bucla e deschisa si va bloca iesirea Vc in "1" logic, aprinzand si LED-ul. Din starea asta se poate scoate doar prin intreruperea alimentarii.

Cam astea ar fi cele constatate practic. Mentionez ca am lasat montajul sa functioneze fixat pe o frecventa oarecare, iar a doua zi dimineata am constatat ca QRG-ul respectiv nu se modificase.

Daca veti executa corect montajul si daca veti avea rabdare sa rezolvati si excursia varicapurilor, atunci puteti fi siguri ca veti obtine exact ceea ce a mentionat si autorul in articol. Totusi, reamintesc ca FLL reprezinta "PLL-ul saracului", asa cum bine spunea un foarte bun prieten de-al meu. Va reusi sa compenseze fuga lenta (termica), dar salturile bruste le va interpreta ca deschidere intentionata a buclei (de exemplu, daca vei tranti un pumn in masa langa placa VFO-ului, frecventa se va deplasa si va fi fixata de circuit la o noua valoare, pe care va tinde s-o pastreze in limitele setate prin firmware). FLL-ul nu va reusi sa egaleze comportamentul unui PLL, dar datorita simplitatii sale, e mult mai bun decat nimic.

Va urez succes si va invit sa postati comentarii prin care sa ne semnalati reusita sau diversele probleme intampinate.

________

73! de Cezar, YO3FHM

{jcomments on}