# Analog Circuit Design

Johan H. Huijsing Rudy J. van der Plassche and Willy Sansen (editors)

Springer-Science +Business Media,

B.V.

#### Analog Circuit Design

# Analog Circuit Design

## Operational Amplifiers, Analog to Digital Convertors, Analog Computer Aided Design

#### Edited by

Johan H. Huijsing T.U. Delft, Delft, The Netherlands

Rudy J. van der Plassche

Radio and Data Transmission Systems, Philips Research, Eindhoven, The Netherlands

and

Willy Sansen K.U. Leuven, Heverlee, Belgium

#### Printed on acid-free paper

#### All Rights Reserved

© 1993 Springer Science+Business Media Dordrecht

Originally published by Kluwer Academic Publishers in 1993

Softcover reprint of the hardcover 1st edition 1993

No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission from the copyright owner.

### **Contents**

| Preface                                                                  | vii        |

|--------------------------------------------------------------------------|------------|

| OPERATIONAL AMPLIFIERS                                                   | 1<br>1     |

| New High Speed Amplifier Designs, Design Techniques and Layout Problems, | 3          |

| The Impact of New Architectures on the Ubiquitous Operational Amplifier, | 25         |

| Design of Low-Voltage Bipolar OpAmps,  Jeroen Fonderie, J.H. Huijsing    | 41         |

| OpAmp Design towards Maximum Gain-Bandwidth,<br>M. Steyaert, W. Sansen   | 63         |

| The CMOS Gain-Boosting Technique,                                        | 87         |

| CMOS Buffer Amplifiers,                                                  | 113        |

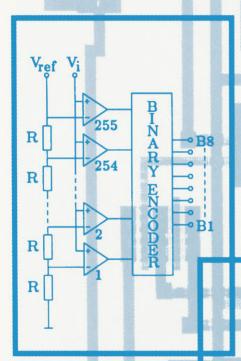

| ANALOG TO DIGITAL CONVERSION                                             | 139<br>139 |

| High Speed Sample and Hold and Analog-to-Digital Converter Circuits,     | 141        |

| High Speed Folding ADC 's,                                               | 163        |

| Oversampled Analog-to-Digital Converters,                                | 185        |

| High Speed 1-Bit Sigma Delta Modulators, Tapani Ritoniemi                                                                         | •••   | 225        |

|-----------------------------------------------------------------------------------------------------------------------------------|-------|------------|

| Continuous Calibration, Noise shaping D/A Conversion,<br>Hans Schouwenaars, Wouter Groeneveld, Corné Bastiaansen,<br>Henk Termeer |       | 239        |

| Bandpass Sigma Delta A-D Conversion,                                                                                              |       | 259        |

| ANALOG COMPUTER AIDED DESIGN                                                                                                      |       | 283<br>283 |

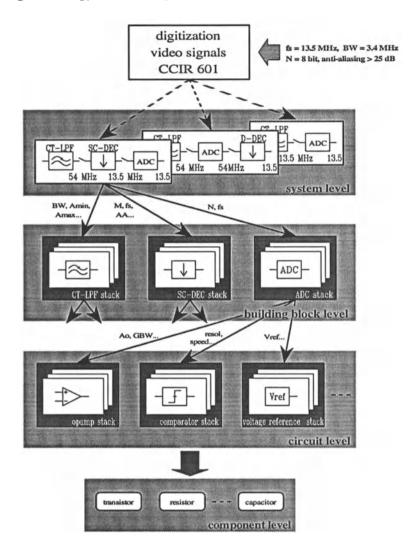

| A Top-Down Constraint-Driven Design Methodology for Analog Integrated Circuits,                                                   |       | 285        |

| Analog Cell-level Synthesis using a Novel Problem Formulation,                                                                    |       | 325        |

| Analog CAD for Consumer ICs,                                                                                                      |       | 347        |

| Tools for Analog Design,                                                                                                          | •••   | 369        |

| Strategies and Routines in Analog Design, E.H. Nordholt                                                                           |       | 391        |

| Open Analog Synthesis System based on Declarative Mod<br>George Gielen, Koen Swings, Willy Sansen                                 | lels, | 421        |

| Index                                                                                                                             |       | 447        |

#### ADVANCES IN ANALOG CIRCUIT DESIGN

# Operational Amplifiers Analog to Digital Convertors Analog Computer Aided Design

#### **Preface**

The fragmented coverage of analog circuits and the restriction to a few sessions at international circuit conferences such as ISSCC and ESSCIRC dissatisfied me for a long time. I would rather have seen a conference fully dedicated to analog circuits.

When it occurred to me that possibly the densest concentration of analog designers in Europe can be found around Philips in Eindhoven, The Netherlands, the idea arose to organize an international workshop on Advances in Analog Circuit Design in Europe. I was happy to find Rudy J. van der Plassche of Philips and Willy Sansen of the Katholieke Universiteit Leuven supporting this idea. Together we successfully organized this workshop.

The main intention of the workshop was to brainstorm with a group of about 50 to 100 analog-design experts on new possibilities and future developments for a few selected topics, and to change this selection year by year. For this first year the three topics that were chosen are:

- Operational Amplifiers

- Analog-to-Digital conversion

- Analog Computer Aided Design.

On each topic six top experts presented tutorials on one day. In this way, a coherent coverage of the field of each topic has been achieved. The tutorial papers on the three topics are now presented in this book.

Kluwer Publishers has decided to yearly publish a volume dedicated to this workshop, containing six tutorial papers on the three topics of the workshop. In this way a valuable series will be built up with a high quality coverage of all important analog areas.

I hope that this first volume will contribute to helping designers of analog circuits.

Johan H. Huijsing Delft University of Technology.

#### **Operational Amplifiers**

#### Introduction

Many interesting design trends are shown by the six papers on operational amplifiers (Op Amps).

Firstly, there is the line of stand-alone Op Amps using a bipolar IC technology which combines high-frequency and high voltage. This line is represented in papers by Bill Gross and Derek Bowers. Bill Gross shows an improved high-frequency compensation technique of a high quality three stage Op Amp. Derek Bowers improves the gain and frequency behaviour of the stages of a two-stage Op Amp. Both papers also present trends in current-mode feedback Op Amps.

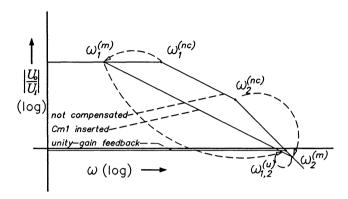

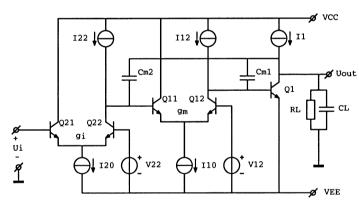

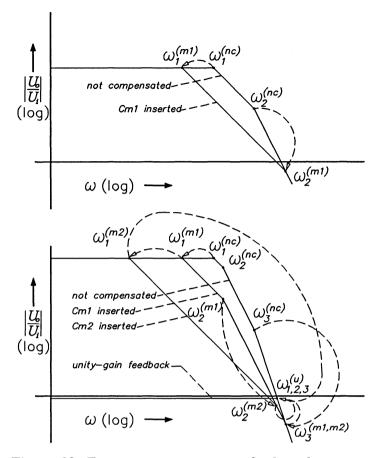

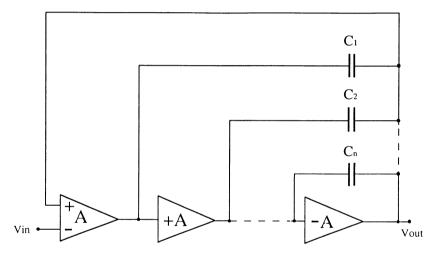

Low-voltage bipolar Op Amp design is presented by Jeroen Fonderie. He shows how multipath nested Miller compensation can be applied to turn rail-to-rail input and output stages into high quality low-voltage Op Amps.

Two papers on CMOS Op Amps by Michael Steyaert and Klaas Bult show how high speed and high gain VLSI building blocks can be realised. Without departing from a single-stage OTA structure with a folded cascode output, a thorough high frequency design technique and a gain-boosting technique contributed to the high-speed and the high-gain achieved with these Op Amps.

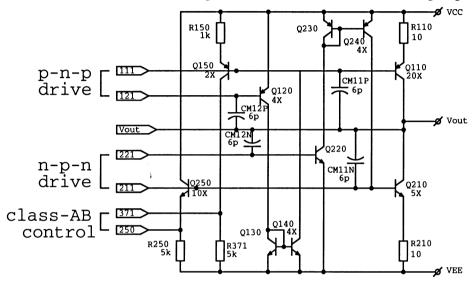

Finally, Rinaldo Castello shows us how to provide output power with CMOS buffer amplifiers. The combination of class A and AB stages in a multipath nested Miller structure provides the required linearity and bandwidth.

Johan Huijsing

# New High Speed Amplifier Designs, Design Techniques and Layout Problems

William H. Gross

Linear Technology Corporation Milpitas, California USA

#### **Abstract**

This paper presents a short review of high speed circuit topologies and several new improvements. The described circuits include both voltage and current feedback amplifiers. Complete amplifier circuits for both complementary and standard bipolar processes are summarized along with techniques for individual amplifier stage implementations. The presentation utilizes intuition and experience more than rigorous mathematics. All of the circuits described have been implemented in silicon.

#### 1. Introduction

Making op amps faster has always been one of the goals of op amp designers. The first op amps were basically DC amplifiers; even voice quality audio was impossible because of the low slew rates. The first monolithic op amps were faster and able to pass voice quality audio without a problem. The introduction of feed-forward and integrated P-Channel JFETs improved the speed of monolithic amplifiers by about an order of magnitude. These amplifiers were more than capable of music quality audio, but still far short of being able to pass video signals. In the last decade, complementary bipolar processes have made possible true video op amps. Non-traditional topologies, such as current feedback, have improved the speed of op amps even more. Today there are many different processes that are used to make high speed op amps. The circuits described

in this paper apply to any bipolar process; however the ultimate speed of the integrated amplifier will be determined by the cutoff frequency of the transistors and the size of the parasitic capacitors and resistors.

#### 2. Speed versus DC Accuracy

The design of all op amps involves many trade-offs. Some of these are well known, such as amplifier bandwidth and slew rate versus supply current, amplifier bandwidth versus transistor cut-off frequency, and slew rate versus minimum closed loop gain. Experienced op amp designers often trade DC accuracy for speed. It is very important when comparing high speed op amps to look at the DC spees. Degenerating the input stage of an amplifier increases the slew rate, but it decreases the DC gain by the same factor. Wafer sort trimming improves the room temperature specifications; but looking closely, what is improved over temperature? The input bias and offset currents often cause larger errors than the offset voltage in trimmed op amps. Input degeneration increases the amplifier's noise voltage.

The input stages described in this paper do not show any resistive degeneration. The circuits will all slew faster with higher tail currents and input degeneration; in fact, most of these circuits were built with resistive degeneration. Often the amplifiers are optimized for closed loop gains greater than one by reducing the amount of resistive degeneration.

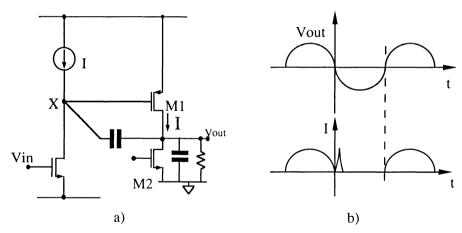

#### 3. Folded Cascode Amplifiers

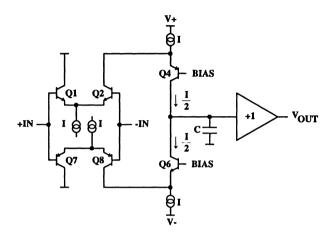

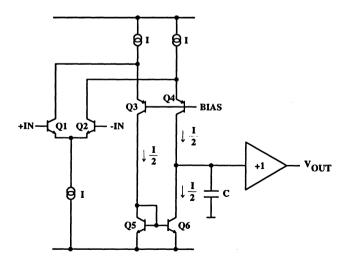

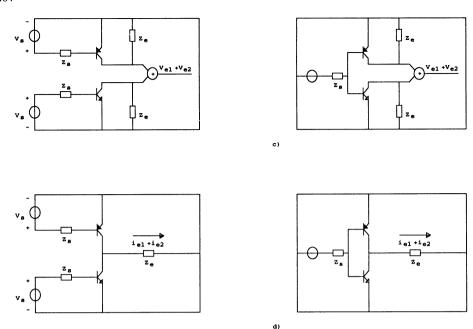

There are many ways to make an op amp, but all have one thing in common: the input stage must have its common mode input voltage independent of the output voltage. The way the signal is "level shifted" from the input to the output is often used to describe and categorize op amps. The fastest way to get the signal from the input stage to the output is with a "folded cascode". This type of level shift feeds the input current into the emitter of a transistor whose collector goes to the input of the output buffer. There are at least two basic ways of implementing a folded cascode: using two input stages in parallel, coming off each single-ended and summing the signals at the output (Fig.1), or using a balanced circuit with a current mirror to convert to single-ended (Fig.2). Both circuits are very fast because there is only one high impedance node and there is no Miller capacitance associated with the inputs. The two-input circuit is

faster because there is no second pole due to the mirror, however in practice the differential circuit is more common because the DC accuracy is much better. High speed op amps with these topologies are usually implemented in complementary processes because the signal is passed by both NPNs and PNPs.

Figure 1: Two input folded cascode.

Figure 2: Balanced folded cascode.

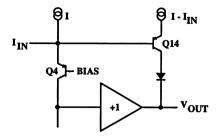

Figure 3: Cascode compensation.

Both versions of the folded cascode circuit have only one gain stage and therefore low open loop gain is a serious problem. To increase the voltage gain requires increasing the impedance level at the compensation node. The output impedance of the cascode transistors (and the mirror output in Fig.2) will limit the gain even if the output buffer isolates the load completely. A very effective way to increase the output impedance of a cascode transistor was described by Cotreau [1] and is shown in Fig.3. The base current of  $Q_{14}$  is added to the emitter current of  $Q_4$  to compensate the loss of  $Q_4$ 's base current. Both transistors operate at the same collector current and have the same base-collector voltage; therefore the two base currents are equal. The circuit has a theoretical mismatch of one divide by beta, but in reality the operating current and transistor beta matching will limit the performance. The circuit will increase the output impedance by ten to twenty times; note that the collector-base capacitance is also cancelled which may enhance AC performance. The disadvantage of this circuit is that it causes offset errors that must be compensated with a similar circuit and it must be done twice for maximum effect. The circuit also increases power dissipation.

Nelson and Feliz [2] described a new way to increase the gain of the balanced folded cascade circuit. Rather than increasing the output impedance of just one transistor, this new circuit increases the impedance at the compensation node. This new circuit does not introduce offset and requires very little power. It does not add to, or cancel the capacitance at the compensation node and therefore does not affect the AC performance.

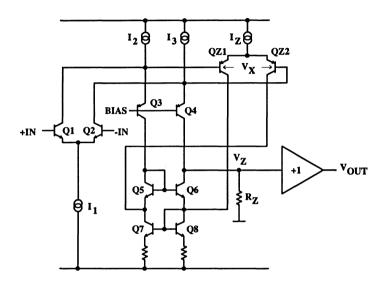

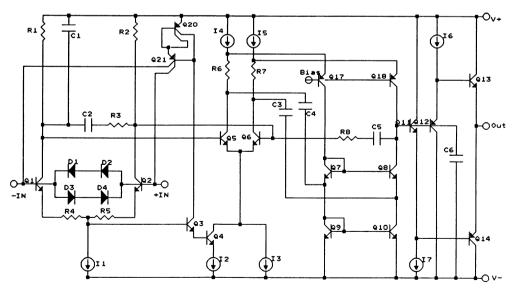

Fig.4 shows the balanced folded cascode circuit with the new gain enhancement circuit  $(Q_{ZI}, Q_{Z2} \text{ and } I_Z)$ .  $R_Z$  represents the equivalent resistance at the high impedance node. The circuit operation is based on sensing the collector voltage of a common base transistor by measuring the changes in the voltage at the emitter. The circuit differentially senses the

voltage change in the base-emitter voltage of the cascode transistors  $Q_3$  and  $Q_4$ . The current that must be inserted into the mirror to compensate for  $R_Z$  so that  $Q_4$ 's collector current does not change is

$$\Delta I = \frac{\Delta V_Z}{R_Z} \tag{1}$$

Figure 4: New improved gain enhancement.

The change in voltage  $V_X$ , due to the change in  $Q_4$ 's collector voltage for a constant collector current in  $Q_3$  and  $Q_4$  is

$$\Delta V_X = V_t \frac{\Delta V_Z}{V_{a,Q_A}} \tag{2}$$

where  $V_{a,Q4}$  is the transistor's Early voltage and  $\Delta V_Z$  is small compared to it. The  $Q_{Z1}$ ,  $Q_{Z2}$  differential current is

$$I_{C,Q_{ZI}} - I_{C,Q_{Z2}} = \frac{\frac{1}{2}I_Z}{V_t} \cdot \Delta V_X = \frac{\frac{1}{2}I_Z}{V_t} \cdot \left(\frac{V_t \cdot \Delta V_Z}{V_{a,Q_4}}\right) = \frac{I_Z}{2V_{a,Q_4}} \cdot \Delta V_Z$$

(3)

We have substituted for  $\Delta V_X$  based on constant collector current in  $Q_4$ . Setting

$$\Delta I = I_{C,Q_{ZI}} - I_{C,Q_{Z2}}$$

(4)

results in

$$I_Z = \frac{2 \cdot V_{a,Q_4}}{R_Z} \tag{5}$$

For the typical case where the output buffer is not contributing to  $R_Z$  and the PNP Early voltage is much less than the NPN Early voltage, we get

$$R_Z = \frac{\beta_{Q_4} \cdot V_{a,Q_4}}{I_{c,Q_4}} \tag{6}$$

Substituting this into the formula for  $I_Z$  gives

$$I_Z = 2 \cdot I_{B,Q_A} \tag{7}$$

This last equation tells us the value of  $I_Z$  should track the inverse of PNP  $\beta$  for optimum gain. There are several ways to generate  $I_Z$ , however using a PNP "pinch" resistor makes trimming practical. This technique typically increases the gain by 25 times, and by at least 10 times over temperature. It should also be noted that the increase in power dissipation is very small.

In the design of high speed amplifiers, and especially single gain stage amplifiers, the amount of capacitance on the high impedance node determines the frequency response, and hence the compensation and stability of the amplifier. Therefore extra care and attention in mask design are required.

High speed amplifier design requires using a circuit simulator such as SPICE. SPICE models the parasitic capacitors associated with transistors very well; when a transistor is stretched or modified in mask design, it is a simple matter to evaluate the effects by modifying the models. Unfortunately the parasitic capacitance associated with the metal traces can be larger than that of the transistors. For this reason the parasitic capacitance due to the metal must be added as a separate component in the simulation. It is usually only necessary to add these capacitors to the high impedance nodes. It is important when characterizing the IC process to use actual measured data of the metal capacitance. The best way is to have a test pattern that allows the area and perimeter contributions to be evaluated as independently as possible. Due to fringing effects, the perimeter of a narrow trace dominates the total capacitance of that trace. It is also important to evaluate fully passivated parts rather that die that have only been processed through metal. The passivation can increase the capacitance of a trace by 20% or more. When debugging a circuit on the

probe station, it is useful to estimate the effects of passivation and still have the benefits of exposed metal. Coat the die with vegetable oil to estimate the additional capacitance due to passivation.

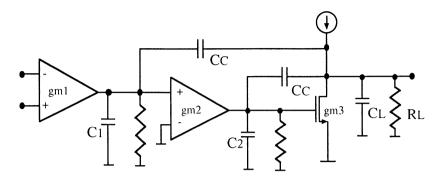

#### 4. Three Stage Amplifiers with Feed Forward

The three stage amplifier is widely used because it results in excellent DC performance and very high gain. Another advantage of the three stage amplifier topology is that the slow PNP level shift transistors found in conventional non-complementary processes are all in one stage and it is easy to use feed-forward to feed the signal around them. Fig.5 shows the traditional topology.

Figure 5: Traditional three stage amp.

Much has been written about this topology and its difficulties, but in a nutshell it has three AC problems. The first is the pole caused by  $C_I$  that is required to make the drive to the second stage single ended; this pole causes a doublet that slows down settling. The second problem is that the signal goes through the mirror of the second stage and therefore it is not as broad-band as it could be; this requires that the feed-forward pole be at a lower frequency and that slows down settling. The last problem is that the feed-forward doublet causes settling problems of its own.

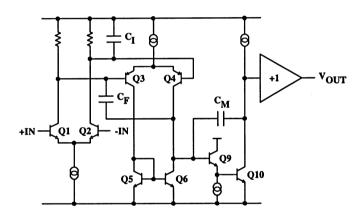

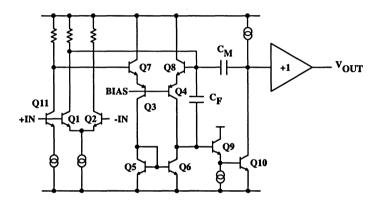

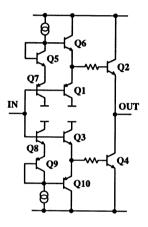

The circuit of Fig.6, first described by Wright [3], eliminates the above three problems. The output of the first stage is single ended to the second stage. There is no connection to the collector of  $Q_2$  and therefore there is no need for an input capacitor. In order to preserve the balanced second

stage and it's inherently low offset, the reference input to the second stage is generated with  $Q_{II}$  and its load resistor. This voltage is identical with the voltage at the collector of  $Q_{II}$ , except there is no signal at the collector of  $Q_{II}$ . Operating the PNPs in a common base configuration eliminates the second problem. There is no signal in  $Q_7$ ,  $Q_3$ ,  $Q_5$  or  $Q_6$ . The speed of the second stage is limited only by the PNP  $Q_4$  (assuming NPN  $Q_8$  is much faster). A doublet is formed by the feed-forward capacitor  $C_F$  and the cutoff frequency of  $Q_4$ . The feed-forward doublet is inside the Miller integrator feedback loop formed by  $C_M$  and the gain stage  $Q_9$  and  $Q_{10}$ . This solves the third problem by reducing the effect of the doublet by the loop gain of the Miller integrator.

Figure 6: Faster three stage amp.

This circuit has been implemented in an 800 MHz, 15 V process with 15 MHz lateral PNPs. The unity gain stable amplifier has a 90 MHz gain bandwidth product and 45 degrees of phase margin. The voltage gain is 45,000 and the settling time to 1 mV is 160 ns.

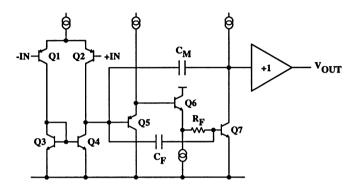

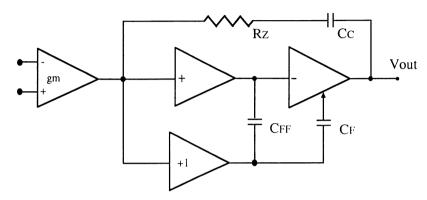

#### 5. Two Stage Miller Integrator Amplifiers with Feed-Forward

The most common op amp topology uses two stages where the second is a Miller integrator. Fig.7 shows how feed-forward can even improve this topology. The input PNP differential amp  $(Q_1 \text{ and } Q_2)$  does not limit the bandwidth of this amplifier when implemented in a complementary process. The amplifier bandwidth is limited by the speed of the Miller integrator formed with  $C_{M2}$  and  $Q_5$ ,  $Q_6$  and  $Q_7$ . The two emitter followers  $Q_5$  and  $Q_6$

increase the gain of the circuit to over a million, but they also add interstage poles. The addition of  $R_F$  and  $C_F$  fixes the problem. Now the integrator is stable and has no "second stage bump" as described by Solomon [4]. This technique is especially useful when the impedance levels of the emitter followers are high because they are running at low currents.

Figure 7: Two stage with feed forward.

#### 6. Current Feedback Amplifiers

Current feedback amplifiers are popular because of their inherent AC advantages: excellent large signal performance and bandwidth that is not a function of closed loop gain. Current feedback amplifiers have a low impedance inverting input that follows the non-inverting input. The feedback is the current that flows in the inverting input. Because the current flows both into and out of the inverting input, fast NPNs and PNPs make the job a lot easier. The most critical blocks in the current feedback topology are the current mirrors that take the feedback current and turn it around into the high impedance node.

The speed of the mirrors determines the speed of the amplifier. There are two AC criteria to use when evaluating current mirrors for current feedback amplifiers. The small signal response determines the bandwidth of the amplifier and the large signal response determines the output slew rate and settling time. One way to evaluate the small signal performance is to note the frequency where a given amount of phase shift occurs, usually 30 degrees or so. The large signal performance is more difficult to quantify, but the maximum current that the mirror can handle before any transistors saturate is a good starting point.

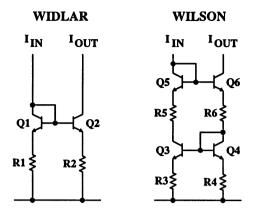

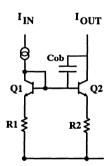

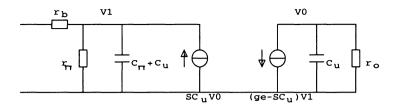

Figure 8: Standard mirrors.

Comparing the response of several mirrors is the first step in designing a current feedback amplifier. The Widlar and Wilson mirrors are shown in Fig.8. The  $R_b$ ,  $C_{in}$  and  $C_{ob}$  of the transistors determine the small signal response of the Widlar mirror. The amount of current the diode connected transistor can handle before it saturates determines the large signal response. The most popular current mirror in current feedback amplifiers is the Wilson mirror because of its excellent DC performance.  $Q_5$  and  $R_5$  are optional to improve DC accuracy.  $R_6$  reduces the amount of feedback and makes the Wilson more stable. Without  $R_6$  or capacitance on the collector of  $Q_3$  there usually is peaking in the small signal response. The peaking will cause gain margin problems in the overall amplifier. The emitter resistors in both mirrors improve the large signal behavior and the DC matching.

Figure 9: Non-saturating mirrors.

Two simple mirrors that do not have saturation problems are shown in Fig.9; these mirrors are not as DC accurate as the first two. The first circuit is the fastest mirror. Only the speed of  $Q_2$  ( $R_b$ ,  $C_{in}$  and  $C_{ob}$ ) limits the small signal response since the emitter follower presents a low impedance drive to the base. The "Witch Hazel" mirror has higher output impedance and has long been used to improve high current lateral PNP current sources. The small capacitor eliminates peaking. The large signal response of these mirrors is excellent since it is not limited by the saturation of any diode connected transistors. The turn off response time is enhanced because the emitter follower actively pulls base current out of the output transistor.

| Conditions              | Widlar | Wilson | Super<br>Fast | Witch<br>Hazel |

|-------------------------|--------|--------|---------------|----------------|

| 0.1mA, 30° phase shift  | 31MHz  | 23MHz  | 57MHz         | 29MHz          |

| 0.25mA, 30° phase shift | 45MHz  | 30MHz  | 67MHz         | 41MHz          |

| 0.5mA, 30° phase shift  | 53MHz  | 34MHz  | 74MHz         | 59MHz          |

| Maximum Current         | 1.5mA  | 1.5mA  | N/A           | N/A            |

Table 1: Comparison of various current mirror circuits.

Table 1 shows the AC data for these mirrors when implemented in a 36 V, 600 MHz complementary process. The emitter degeneration resistors were fixed at 400  $\Omega$ ; the bias current sources in the Super Fast and Witch Hazel mirrors were set to 100  $\mu A$ . All the mirrors were compensated for flat amplitude response while driving a capacitive load of 5 pF.

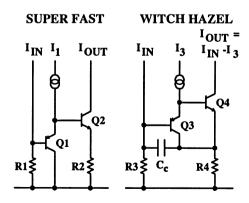

The availability of complementary bipolar processes made monolithic current feedback amplifiers practical. The first monolithic current feedback amplifiers were basically implementations of discrete designs; they did not take advantage of the inherent matching of the NPNs and PNPs of a complementary process. The circuit of Fig.10 shows a very simple and very fast current feedback amplifier.

The circuit uses the simplest input stage possible, just four transistors, and the super fast current mirrors. What sets this circuit apart from others

<sup>&</sup>lt;sup>1</sup>The origins of the name "Witch Hazel" are lost. It was common usage in the early 1970s at Motorola.

is the unusual biasing scheme. A floating current source feeds a diode connected NPN  $(Q_1)$  whose base-emitter voltage is impressed upon a PNP base-emitter  $(Q_2)$ . The collector current of the PNP is therefore the current source times the ratio of the PNP beta divided by the NPN beta. The input stage current will vary plus or minus 50% with processing.

Figure 10: Very fast current feedback amplifier.

The advantage of this biasing scheme becomes apparent when we notice that the  $V_{be}$  of PNP  $Q_5$  is now the same as the  $V_{be}$  of NPN  $Q_1$ . This means that the  $V_{be}$  of PNP  $Q_5$  is going to match the  $V_{be}$  of NPN  $Q_6$  and the circuit will have low input offset voltage. Notice that the same is true of  $Q_3$ ,  $Q_4$ ,  $Q_7$  and  $Q_8$ . In practice this improves the input offset by a factor of three over the same circuit with constant currents feeding  $Q_5$  and  $Q_7$ . The collector currents of  $Q_5$  and  $Q_7$  are then used in the current mirrors. Again the  $V_{be}$  of  $Q_{11}$  is now set by an NPN  $(Q_1)$  and it therefore matches the  $V_{be}$  of  $Q_{12}$ . This improves the DC accuracy of the mirror by six times compared with feeding  $Q_9$  and  $Q_{11}$  with constant currents. Significantly improved accuracy can be obtained by cascoding  $Q_2$  and  $Q_4$  at the expense of input common mode range. This circuit, without the cascodes, has been implemented in a 36 V, 600 MHz complementary process. The resulting amplifier operates on supplies from  $\pm 2$  V to  $\pm 15$  V and has a bandwidth of 140 MHz with an output slew rate of 1100 V/ $\mu$ s. The circuit is fast because it is simple. It is accurate because of the unusual biasing.

#### 7. Output Buffers

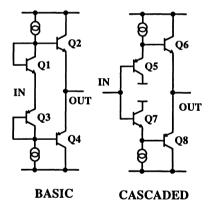

Almost all op amps have output buffers that isolate the load from a high impedance node. High speed op amps are no exception and they usually have to drive larger output currents than slower op amps. This is because high speed op amps are often used to drive cables and other low impedance loads as well as lower values of feedback resistors. All the high speed output buffers are based on the simple emitter follower. The fastest and most interesting output buffers use complementary NPNs and PNPs.

Fig.11 shows the basic complementary emitter follower output stage and the widely used cascaded complementary emitter follower stage. The basic stage isolates the load from the high impedance node with the current gain of the NPN or the PNP, depending on which is conducting the most current. At high frequencies, the gain is determined by the cutoff frequency of the transistors. To minimize second harmonic distortion requires the gain (and therefore the cutoff frequency) of the NPN and the PNP to match reasonably well. Because the basic stage has only one beta of isolation, it is very fast and well behaved, even into capacitive loads.

Figure 11: The basic buffers.

The cascaded stage is very popular because it isolates the load with an NPN times a PNP current gain when the output is both sinking and sourcing current. This improves the second harmonic distortion and of course the additional isolation increases the amplifier's gain. This output stage is quite well behaved and usually does not require any additional components to stabilize, even with capacitive loads.

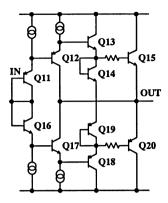

Fig.12 shows a modification to the cascaded stage<sup>2</sup>. This buffer has the same isolation as the cascaded stage, but requires less quiescent current thanks to  $Q_6$  and  $Q_{10}$ . There is an important improvement in this circuit compared to the previous circuit where the outputs ( $Q_2$  and  $Q_4$ ) were made into darlingtons.  $Q_1$  and  $Q_3$  pull base current out of the output transistors to prevent them from destroying themselves during high frequency, large signal conditions. This output stage is well behaved, but it will peak more than the previous two buffers. The resistors in series with the output transistor bases slow the output stage a little, but improve the ability to drive capacitive loads a lot.

Figure 12: Modified cascade buffer.

There are times when more load isolation is required. In order to drive lower impedance loads with the same accuracy, or to improve accuracy into standard loads, requires raising the impedance at the input of the buffer. Fig.13 shows a buffer with the current gain of three transistors isolating the load. Again the resistors improve the circuit's ability to drive capacitive loads. The diode connected transistors  $Q_{14}$  and  $Q_{19}$  must be large enough to remove the output transistors' base current during large signal high frequency operation without saturating or excessive power dissipation will result.

<sup>&</sup>lt;sup>2</sup>First used in the EL2002 IC.

Figure 13: Triple buffer.

Figure 14: The fix for capacitive loads.

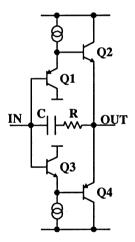

Recently several high speed amplifiers have been introduced that are stable with any capacitive load. Fig.14 shows the way most of these amplifiers accomplish this amazing feat. The capacitor and resistor are boot-strapped when there is a light load on the output, so with a light load, they have no effect on the amplifier's frequency response. When a capacitive load is applied, current flows in the output stage to drive it. This

causes a difference between the input and output of the buffer and that voltage is forced across the capacitor and resistor. The current flowing in the capacitor and resistor comes from the high impedance node and it is therefore loaded. Another way to look at this is to note that a large enough output capacitance will result in no AC signal at the output; then the capacitor and resistor will load the high impedance load directly adding a pole and a zero. This loading slows the amplifier, reduces its gain and broad-bands the high impedance node making the amplifier stable. Unfortunately this technique cannot tell the difference between a resistive and a capacitive load. Amplifiers with this circuit do not drive low impedance loads well. Do not use this technique in video cable driver circuits.

Composite video amplifiers must keep their frequency response as constant as possible when the output DC level changes. The parameters that measure this performance are called differential gain and differential phase. The main causes of differential gain and phase errors are: non-linear input stage transconductance, the voltage coefficient of junction capacitors, and changes in the output impedance. The input stage transconductance is usually linearized with resistive emitter degeneration. In current feedback amplifiers the external feedback resistor acts as the transconductance stage and therefore they are usually very linear. The change in junction capacitance on the high impedance node is usually the major contributor to differential gain and phase errors when the amplifier is lightly loaded. Dielectrically isolated processes make excellent video amplifiers because they do not have the voltage dependent collector-substrate junction capacitance on the high impedance node.

The output stage determines how much the load affects the frequency response. Running a lot of quiescent current in the output stage reduces the output impedance; more importantly it also reduces the amount of change in the output impedance as the output drives the load. The output impedance forms a voltage divider with the load resistor and therefore must be constant for the gain to remain constant. This change in output impedance is a major cause of differential gain and phase errors in video cable driver amplifiers.

#### 8. Current Sources and Cascodes

There probably are an infinite number of ways to make current sources for op amps. In high speed op amps, the current sources and cascode transistors slew quickly and should not generate any problems. When the collector of a transistor slews, the current that charges and discharges the collector-base capacitance must flow out of the base.

This base current is often as large as the collector current and the normal guidelines used to design for DC performance will not necessarily deliver good AC performance.

The AC performance of the simple Widlar mirror (Fig.15) with a constant input current is quite good. When the collector of  $Q_2$  slews, the additional base current is mirrored and shows up as collector current. The amount of additional current  $Q_1$  can take before it saturates limits the positive slew rate.  $I_{IN}$  limits the negative slew rate; when the slew induced base current is equal to it, the circuit turns off. Exceeding the slew rate the circuit can handle causes recovery delays and degrades the settling time of the amplifier. The input current and the current gain of the mirror should be optimized for the slew rate required at the collector. For symmetrical slew rate limits,  $Q_1$  should not saturate at twice  $I_{IN}$ . A disadvantage of this simple circuit is its output capacitance. The collector-base capacitance of  $Q_2$  is multiplied by the current gain of the mirror. Replacing  $Q_1$  and  $R_1$ with three series connected Schottky diodes makes for an interesting variation of this current source. The Schottky diodes reduce the gain of the mirror and therefore lower the output capacitance. There is no limit on the positive slew rate because Schottky diodes do not saturate. The negative slew rate limit is unchanged.

Figure 15: Current source dynamics.

Biasing the current source transistor base with a very low impedance that can sink and source a lot of current results in the highest slew rates and the lowest power dissipation. The low impedance on the base eliminates the multiplication of the collector-base capacitance and therefore minimizes the

capacitance that has to be slewed. Fig.16 shows an excellent implementation of this concept.  $Q_5$  and  $Q_6$  form a class AB output stage that drives  $Q_7$ . They can be operated at a lower quiescent current than the slew induced base current of  $Q_7$  and still the base voltage will not move much.

Figure 16: Biasing current source.

$Q_6$  must be large enough not to saturate during positive slews. Additional capacitance on the base of  $Q_5$  (and  $Q_6$ ) reduces the amount of input current required; the collector-substrate capacitance of  $Q_3$  (and  $Q_4$ ) is an excellent source. Of course cascode transistors benefit from this class AB bias technique as well.

#### 9. Power Dissipation and Temperature Coefficients

The biggest influence on the slew rate of high speed amplifiers is the amount of current available. If unlimited supply current were available, amplifiers would go faster. In most ICs, package dissipation limits the maximum supply current a designer can use without exceeding the maximum reliable junction temperature. This is especially true when the package of choice is the SO-8! Designing for a lower supply voltage is an obvious way to get more current without exceeding the package limitations. The junction capacitors get larger (and more non-linear) as the supply voltages drop; however the increase in current available usually will more than make up for it. Lower supplies also reduce the dynamic range of the amplifier; to make up for this, the circuit design becomes more difficult,

especially when cascodes are required.

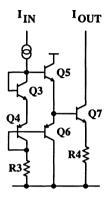

Figure 17: Typical bias current generator.

When considering power dissipation, it is important to pay attention to the temperature coefficient of the currents in the amplifier. Traditional op amp designs use " $\Delta V_{be}$  over R" or PTAT³ biasing. This minimizes the offset drift of the amplifier. Unfortunately it also increases the power dissipation of the amplifier at high temperature. In most linear IC processes, the collector resistance of the transistors determines the maximum current they can carry. With PTAT biasing, the transistors are at a double disadvantage; the current is maximized when the transistor's  $R_C$  is maximized. In order for the amplifier to perform well hot, the transistors must be sized large enough not to saturate. The larger the transistor, the more capacitance it has and the slower the circuit.

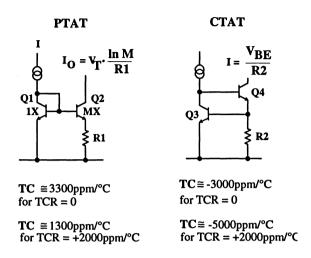

The obvious way to minimize the transistor's size is to operate the transistor with a current that keeps it from saturating. This requires that the current reduce with temperature since the collector resistance increases with temperature. The popular " $V_{be}$  over R" or CTAT<sup>4</sup> biasing scheme is a good way to minimize transistor size. Fig.17 shows simple PTAT and

<sup>&</sup>lt;sup>3</sup>PTAT is an acronym for Proportional To Absolute Temperature.

<sup>&</sup>lt;sup>4</sup>CTAT is an acronym for Complementary To Absolute Temperature.

CTAT biasing circuits and gives the approximate temperature coefficients for each with both thin film (TCR = 0 ppm/°C) and base (TCR = 2000 ppm/°C) resistors. In an amplifier with a maximum junction temperature of 150 °C, using CTAT biasing with base resistors will reduce the required transistor's capacitance by a factor of two compared to PTAT biasing.

#### 10. Cross Talk

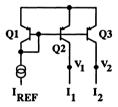

Very often high speed amplifiers exhibit strange frequency response or oscillations because the bias circuitry is reacting with the AC signal circuitry. The most perplexing of these problems is caused by coupling between amplifier stages through common biasing. Fig.18 shows the most common way to make multiple current sources. As discussed in the previous section, the collector-base capacitance of  $Q_2$  will send a signal into  $Q_1$  that will mirror into  $Q_3$ ! This is a small signal as well as a large signal problem;  $V_1$  will talk to  $V_2$ . This can cause problems even when a very low impedance is driving the bases of  $Q_2$  and  $Q_3$ .

Figure 18: Common bias.

In the beginning phases of a high speed amplifier design, use completely separate bias generators for each stage of the amplifier. Keep the bias generators separate if the total power dissipation and die size are not severely impacted by this "additional" overhead. When combining bias circuitry, be sure to keep the output stage separate from the input. It is very hard to "debug" slow settling time when it is caused by the output slew affecting the input bias circuitry.

A last note of caution: dual and quad amplifiers that share common bias circuitry will almost certainly talk to each other. A pair of 100 MHz amplifiers in one package is enough trouble; do not compound it with common bias problems.

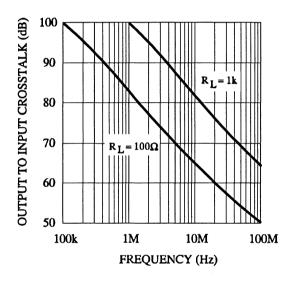

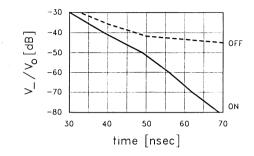

One of the most unexpected cross talk problems is caused by the mutual inductance between wire bonds in the package. When current flows in a wire bond, it magnetically couples to the other wire bonds; the result is a voltage source in series with each of the bonds. The wire bonds that carry the output current are the sources of this problem. The amount of voltage generated in the other bonds is proportional to the current in the output. Fig.19 shows the crosstalk from the output of one amplifier to the input of the other amplifier for a dual 120 MHz current feedback amplifier IC. The data is for the die in a 8 pin DIP package with the standard dual op amp pin-out. The data was taken with both 100 ohms and 1 kohm loads to show the output current dependence.

Figure 19: Output to input cross talk.

In application specific circuits where the pin-out is not defined by history, the differential inputs should be next to each other with parallel wire bonds. The output and supplies should be on the other side of the die with wire bonds parallel to the inputs. This will minimize the crosstalk.

#### 11. Summary

High speed amplifier development is an exciting area of monolithic circuit design because the successful circuit techniques are the ones that are

totally interwoven with the new process capabilities. The next big improvement in high speed amplifiers will involve not just new circuits, not just new processes, but the synergy that comes from both. The general purpose and precision amplifier design techniques already learned are the necessary foundation to build on for high speed amplifier design. The knowledge of good DC circuit design is important in high speed amplifier design because doing more with less (transistors) is the way to faster amplifiers. The 1970s saw enormous growth and development of general purpose op amps, the 1980s were the decade of precision op amps and the 1990s will be the decade of the high speed op amps. The fun is just beginning.

#### References

- [1] Gerald M. Cotreau, "An Opamp with 375 V/µs Slew Rate, ±100 mA Output Current" 1985 International Solid State Circuits Conference.

- [2] Carl Nelson and George Feliz, "LTC internal patent application".

- [3] John Wright, "The LT1190 Family, A Product of Design Innovation," Linear Technology, vol.1, no.2, pp.3, 11, 12, 15 October 1991.

- [4] James Solomon, "The Monolithic Operational Amplifier: A Tutorial Study," *IEEE J. Solid-State Circuits*, vol. SC-9, no.6, December 1974, pp.314-332.

#### Biography

Bill Gross is a Design Manager for Linear Technology Corporation, heading a team of design engineers developing high speed amplifier products. Mr. Gross has been designing integrated circuits for the semiconductor industry for 20 years, first at National Semiconductor, including three years of living and working in Japan, and later at Elantec. He has a B.S.E.E. from California State Polytechnic University at Pomona and an M.S.E.E. from the University of Arizona at Tucson. Mr. Gross is married and the father of two teen-age sons, whose sports activities keep him quite busy.

#### The Impact of New Architectures on the Ubiquitous Operational Amplifier

D. F. Bowers

Analog Devices Inc. (PMI Division)

Santa Clara, California

USA

#### **Abstract**

The operational amplifier has steadily evolved since its inception almost fifty years ago. Sometimes though, radically new architectures appear to fill market requirements. Also, the availability of new I.C. processes such as BiCMOS and Complementary Bipolar yield components which have not previously been available to the op-amp designer. This paper is a review of some recent and not so recent developments.

#### 1. Introduction

The term "operational amplifier" was first used in a paper by Ragazzini et al. in May 1947 [1], though op-amps were (at least) in some use during the Second World War years; notably by Lovell and Parkinson in the development of the Western Electric (Mk.9) electronic anti-aircraft gun director. Monolithic op-amps emerged in the mid 1960's, notably those designed by Bob Widlar at Fairchild. By 1968 he had designed the LM101 [2] (at National Semiconductor), and this product set a standard topology for many future monolithic op-amps.

Much of the progress in monolithic op-amp performance has since then been evolutionary in nature. Process improvements, such as complementary bipolar processing and the bipolar-compatible JFET have definitely led to better op-amps. Design tricks such as feedforward compensation, slew-enhancement and all-NPN output stages have also been great contributors. This paper looks at some of the more radical departures from mainstream op-amp design.

#### 2. The Precision Op-Amp

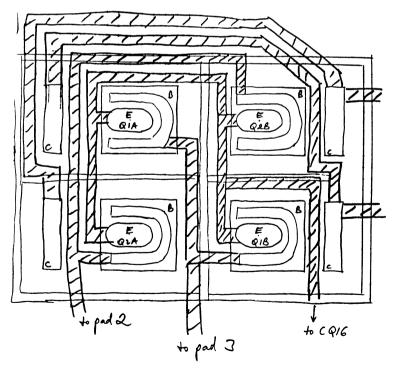

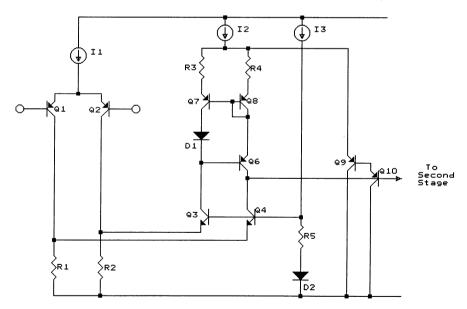

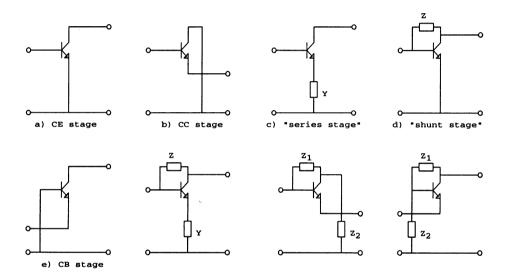

One of the first departures from the LM101 type "two-stage" topology was the  $\mu$ A725 designed by George Erdi at Fairchild in 1968 [3]. Several new concepts were added to this design to improve the precision performance. First, three gain stages were used to improve the overall open-loop gain. This also enabled a relatively low gain resistively-loaded input stage to be used, which can be shown to give the best offset and drift performance. Second, it was realised that gain can be limited by thermal feedback from the output stage to preceding stages. This was overcome by using a layout which was "thermally symmetric" with respect to critical transistor pairs. Third, a "cross-coupled quad" input stage (Fig.1) was used to improve the offset voltage.

Figure 1: Cross-coupled quad technique (this is George Erdi's original hand sketch for the OP-27 input stage).

The theory here is that this arrangement substantially cancels process and thermal gradients across the chip by providing a common-centroid for the input stage pair. The real breakthrough in improving offset, however, came with the development of offset voltage trimming. In the late 1960's it was discovered (at Fairchild) that if the base-emitter junction of a bipolar transistor was avalanched at high current, then a permanent short would result. It was realised at Intersil and Precision Monolithics in the mid 1970's that such an effect could provide on-chip adjustment for integrated circuits. The natural first use of this technique was to trim the offset voltage of precision op-amps, and it became known as "zener-zapping".

"Zener-zapping" was applied to the PMI OP-07 in 1975 [4], where small zeners were used to short out portions of the input stage load resistors. This resulted in an offset voltage of less than 100  $\mu$ V. Meanwhile, Analog Devices had been working along different lines.

Since 1973 they had been trimming thin film resistors by means of a laser, but these trims had been performed after devices were packaged (but not capped). In 1975 they adapted a Teradyne W311 laser trim system to perform trims at wafer level. This enabled them to compete in the OP-07 market place, and they came out with the AD-510 op-amp in 1976 with an offset specification of 25  $\mu V$  maximum.

A few years ago our marketing department decided that the marketplace needed a quad precision op-amp with the same specifications as the OP-07, except that they wanted ten times the gain and the same power consumption for all four amplifiers as a single OP-07. This obviously demands a different approach.

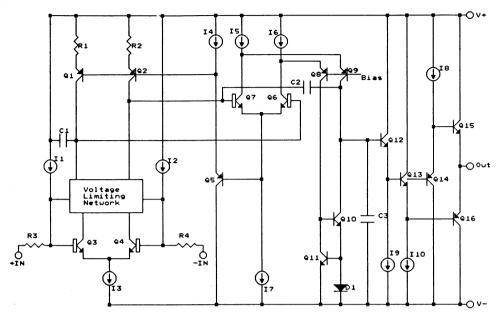

First, in the interests of power consumption and die area, I decided that one of the gain stages had to go, which left two gain stages to provide the target open-loop gain of five million. Fig.2 shows the simplified schematic of what eventually became the OP-400.

Superbeta transistors  $Q_3$  and  $Q_4$  are used in the input stage to achieve a low input bias current. These are cascoded by a voltage limiting network which is merged with the input protection devices to reduce the die size. An active load  $Q_1$  and  $Q_2$  provides a very high stage gain ( $\approx 10,000$ ), and is regulated via a feedback loop consisting of  $Q_5$  and the second stage transistors. Normally, to avoid degrading the first stage gain, emitter followers would be used to buffer the second stage. These, of course increase power consumption and die size. If a folded-cascode is used as the second stage, transistors  $Q_6$  and  $Q_7$  see very little collector-base voltage, and can be made superbeta types also, removing the need for the followers. Finally, a triple-buffered output stage is used to maintain the gain with resistive loads on the amplifier. This architecture meets all the

specifications of an OP-07, but with a gain of 10,000,000 and a supply current of 500  $\mu A$  per amplifier.

Figure 2: Simplified OP-400 schematic.

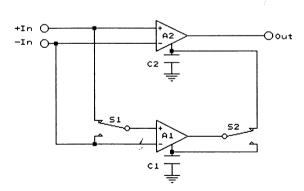

Figure 3: Chopper stabilised op-amp scheme.

The modern precision op-amp has errors almost as low as basic transistor physics will allow, and there does not seem to be room for any real break-throughs in this area. One area where the precision bipolar op-amp has seen some competition is from chopper stabilised amplifiers. The most used configuration is shown in Fig.3, and this evolved from the Harris HA2900 introduced in 1973. Amplifier  $A_I$  spends half the time nulling its own offset, caused by shorting the inputs together with an MOS switch  $(S_I)$  and applying feedback to an internal amplifier point. When  $S_2$  is opened,  $C_I$  stores the amount of feedback necessary to produce the null, and the amplifier is theoretically offset free. For the other half of its time,  $A_I$  nulls the main amplifier,  $A_2$ . Capacitor  $C_2$  stores the voltage needed to null the main amplifier when  $A_I$  is nulling itself.  $A_2$  is thus continuously available for use in normal op-amp configurations. It is normal to integrate such amplifiers on a CMOS process, since the switches are available and MOS inputs can be used to obtain low input currents. Early versions used external storage capacitors and ran at frequencies of a hundred Hertz or so, but the modern trend is to provide internal capacitors with much higher chopping frequencies; 10 kHz being not uncommon.

Bipolar op-amp designers (such as myself) love to point out all the problems associated with chopper stabilisation; input current glitches, intermodulation distortion, overload recovery problems et cetera, but nevertheless these amplifiers do serve a large portion of the market.

#### 3. Improving Speed

High speed amplifiers are the biggest current growth area of the op-amp marketplace. However as Bob Widlar once pointed out [5], "No one can dispute that zero offset, no input current, infinite gain, and the like are desirable characteristics. However, a little practical experience quickly demonstrates that infinite bandwidth is not an unmixed blessing". We have some customers that use our micropower op-amps because they are slow, giving reduced high frequency noise and good tolerance to stray capacitance. But the whole electronic world seems to be moving toward higher speed, and op-amps are definitely no exception.

Obviously, the basic concept for obtaining high bandwidth in an op-amp is to minimise the phase delay through the amplifier. Increasing the stage currents is a fairly straightforward method of reducing the phase delay, but unfortunately amplifiers such as the LM101 which use lateral PNP transistors for level shifting cannot be made faster than about 2 MHz, because of the large transit time of these devices. Two techniques are currently used to circumvent this problem; one is feedforward compensation, the other is to include a faster PNP transistor.

Feedforward compensation involves bypassing the lateral PNP transistor

at high frequencies by means of a capacitor. Fig.4 shows the most used technique for achieving this, as found on products such as the LM118, OP-27 and LT1028.  $C_1$  is the dominant pole compensation capacitor, while  $C_2$  provides a bypass function around the entire second stage.  $C_3$  serves to reduce "peak-back" of the output stage at high frequencies.

Figure 4: Feedforward compensation.

Figure 5: Simplified OP-470 schematic.

Unfortunately, this type of compensation produces a pole-zero pair in the

open-loop response. This leads to excessive settling times, and some ingenious solutions to this problem have been proposed [6]. However, this pole-zero doublet can be avoided altogether by using charge conservation techniques.

Fig.5 shows the feedforward technique used on the OP-470 series of amplifiers. Following the input stage,  $Q_5$  and  $Q_6$  comprise the second stage input pair driving a folded cascode pair,  $Q_{17}$  and  $Q_{18}$ . Two capacitors,  $C_3$  and  $C_4$  provide a bypass function, but they feed into low impedance points created by the load transistors  $Q_8$  and  $Q_9$ . At low frequencies, most of the signal currents in the input pair pass through  $Q_{17}$  and  $Q_{18}$ , but at high frequencies the signal path is through  $C_3$  and  $C_4$ . The point is that at all times the difference in collector currents of  $Q_5$  and  $Q_6$  somehow gets to the collector of  $Q_8$ , even if the internal nodes have not settled. Using this scheme, settling tails at the 12-bit level are not apparent.

Several manufacturers have decided to explore the alternative route of including a high-speed PNP transistor on their process. Radiation Incorporated, now part of Harris Semiconductor, were the pioneers in this respect with their dielectric isolation process. Amplifiers from Harris generally used a single gain stage with a foldback cascode load, and this has set a general trend for amplifiers where highest possible bandwidth is needed. Today, many complementary bipolar processes are in use, falling basically into two categories. Those intended for 36 V operation have  $F_t$ 's of up to 600 MHz, with lower voltage processes often having  $F_t$ 's of several GHz. Using such processes, amplifiers with several hundred megahertz of bandwidth are becoming common.

## 4. Large Signal Performance

Even when a high small signal bandwidth is achieved, a further speed limitation is the slew rate of the amplifier. This can cause drastic limitations on the large signal bandwidth and settling time of an op-amp. For an amplifier with a simple bipolar input stage and dominant pole compensation, it is easy to show that the slew rate is only around 1 V/µs for each 3 MHz of small signal bandwidth. This would mean, for example that a 100 MHz amplifier driving 5 V r.m.s. would have a full-power bandwidth of less than 1 MHz. Traditional methods of improving the slew rate have concentrated on reducing the input stage transconductance so that smaller compensation capacitors can be used [7]. This unfortunately reduces DC accuracy and increases noise. Historically there have been some new architectures devised to improve this situation, one notable

example being the class AB input stage of W. Hearn [8], which eventually turned into the Signetics NE531. More recently, some other interesting techniques have been devised.

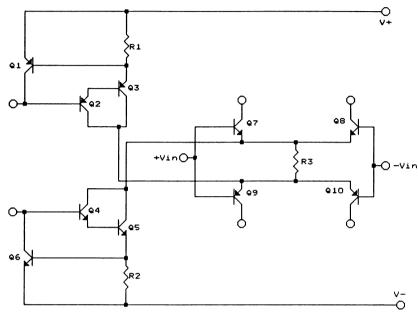

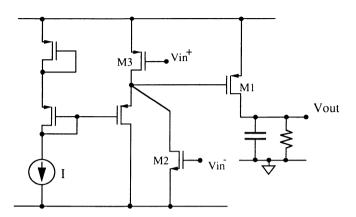

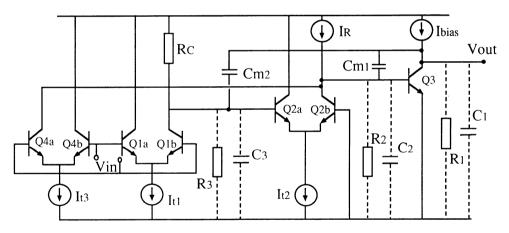

Fig.6 shows an ingenious example using complementary technology [9].

Figure 6: Slew-enhanced complementary input stage.

Figure 7: Simplified OP-275 schematic.

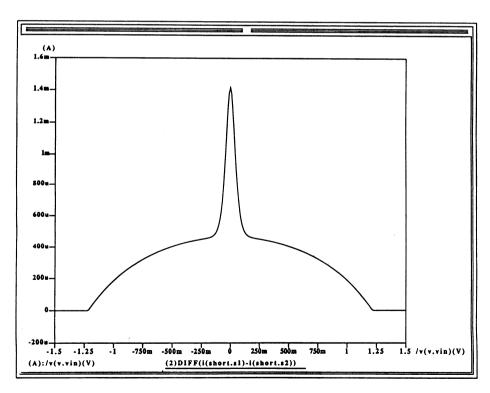

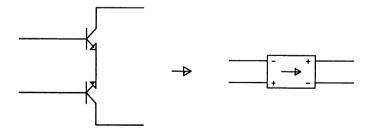

$Q_7$ - $Q_{10}$  are used as a double input stage (actually only one needs to be used to convey the signal, the output from the other being discarded) biased to a  $V_{be}$  proportional current by the remaining transistors.  $R_3$  is scaled to rob some of the biasing current, and partly controls the small signal bandwidth. With large differential inputs,  $R_3$  increases the total currents in both pairs, greatly improving the slew rate. Another surprisingly simple technique is reflected in the simplified schematic of the new OP-275, designed by Jim Butler at PMI (Fig.7). The input stage consists of both a JFET and a bipolar transistor pair in parallel. The tail currents are ratioed 8:1, resulting in both pairs having roughly equal transconductance.

The overall transconductance versus differential input voltage is shown in Fig.8. It can be seen that for small inputs the transconductance is high, but it is still finite with large differentials. This enables the amplifier to have the high slew rate associated with a FET input amplifier, combined with noise and precision approaching that of a purely bipolar design. If ultra high slew rate is needed, it is difficult to beat the class of amplifiers known as *current feedback*.

Figure 8: Transconductance versus input voltage for compound input stage.

#### 5. Current-Feedback Amplifiers

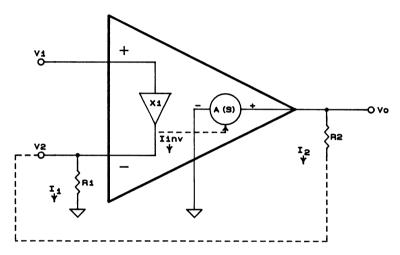

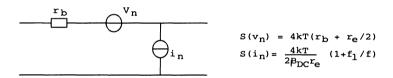

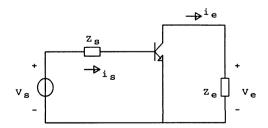

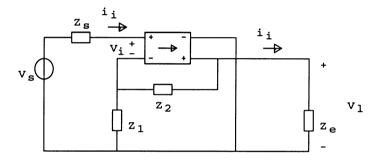

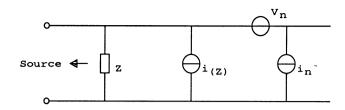

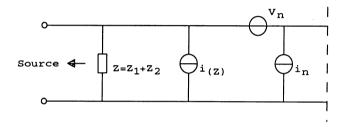

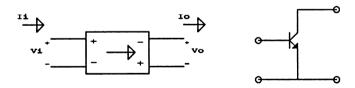

Current feedback op-amps differ from voltage feedback types in that the current supplied to the compensation capacitor is equal to the current flowing in the inverting input. Fig.9 shows the simplified current feedback op-amp model.

Figure 9: Conceptual current feedback op-amp model.

The input stage is now a unity-gain buffer forcing the inverting input to follow the non-inverting one. Thus, the inverting input is a low impedance point capable of accepting current and transferring it to the compensation capacitor. Feedback is always treated as a current and because of the low impedance at the inverting terminal, there is always a feedback resistor, even at unity gain. Voltage imbalances at the inputs thus cause current to flow in or out of the inverting input buffer. These currents are sensed internally and transformed into an output voltage. The transfer function of this transimpedance amplifier is A(s); the units are in ohms.

If A(s) is high enough (like the open loop gain of a conventional op-amp), at balance no net current flows into the inverting input. Therefore all the usual op-amp static equations for closed loop gain can be used. However, the dominant pole now has its time constant set by the product of the *feedback resistor* and an internal compensation capacitor value. If

a fixed feedback resistor is used, the closed loop bandwidth is therefore theoretically independent of gain. In practice finite output impedance in the buffer reduces the bandwidth at very high gains, but it is still a considerable improvement over the conventional op-amp.

The other big advantage of the current feedback architecture lies in its large signal characteristics. No matter how large the input step becomes, the buffer theoretically follows it. This forces the difference between the input and output voltages directly across the feedback resistor. Thus the current available for slewing is proportional to the error voltage, which is exactly the same as saying that the large-signal and small-signal bandwidths are identical. In practice, a variety of second order effects does give a finite slew rate limit, but it is often thousands of Volts per microsecond.

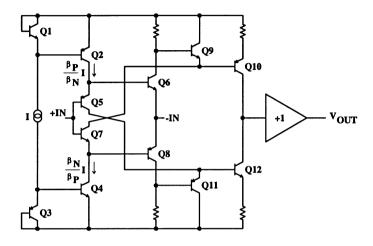

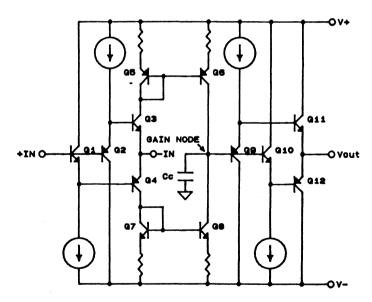

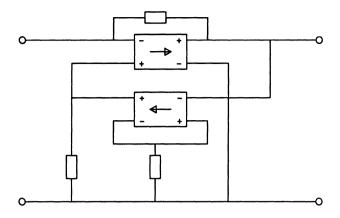

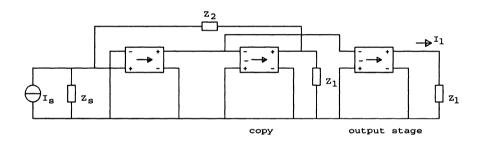

Fig.10 shows a method for implementing such an amplifier, and in fact the majority of commercially available current feedback op-amps are variations on this topology.

Figure 10: Basic implementation of the current feedback op-amp.

$Q_1$ - $Q_4$  form the input buffer which forces the inverting terminal to the potential of the non-inverting one. Any imbalances in the collector currents of  $Q_3$  and  $Q_4$  are summed at the gain node, via current mirrors  $Q_5$ - $Q_8$ , causing the output buffer,  $Q_9$ - $Q_{12}$  to move. Negative feedback via the

feedback resistor corrects the imbalance thus forcing a constant error current (ideally zero) into the inverting input. One problem with this implementation is that Early effects in  $Q_1$ - $Q_4$  cause poor common mode rejection, as low as 50 dB on some available devices. This can be corrected by extensive cascoding but this tends to reduce the AC performance, particularly in the non-inverting mode. Another problem is that good NPN to PNP  $V_{be}$  matching is required to obtain low offset voltage. This can be alleviated by several design tricks, one being to add diodes of the opposite polarity in series with the emitters of each of the input transistors.

#### 6. Voltage Feedback Revisited

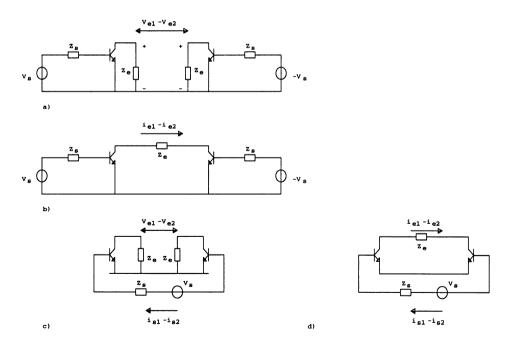

If a second input buffer is added to a current feedback op-amp a voltage feedback amplifier results with similar slewing characteristics to a current feedback type. Fig.11 illustrates the concept, used on the PMI OP-467.

Figure 11: Simplified OP-467 schematic.

$Q_5$ - $Q_8$  form the equivalent of the current feedback input buffer, while  $R_2$  is the equivalent of the feedback resistor. This resistor is preceded by a second buffer consisting of  $Q_I$ - $Q_4$ , identical except for the fact that its output current is discarded. As previously, the full error voltage can be impressed across  $R_2$  and all of this is available to charge the compensation

capacitors,  $C_2$  and  $C_3$  ( $C_1$  and  $R_1$  compensate for the inductive behaviour of the input buffers). A side benefit of this arrangement is that the errors of the buffers tend to cancel, resulting in good DC performance. This topology has been used to create an op-amp capable of operating on 36 V supplies with 35 MHz of bandwidth, 200 V/ $\mu$ S of slew rate and 2 mA of supply current. Noise is 6 nV/ $\nu$ Hz, and offset is below 500  $\mu$ V.

## 7. Single-Supply Amplifiers

As more systems are being powered from single supplies, the need for op-amps with wide voltage range capability becomes critical. To meet this need, a number of op-amps have appeared with signal handling capability including the negative supply rail, and occasionally both supply rails.

Early single-supply amplifiers used Darlington PNP input stages, as there is ample room to fit a conventional active load beneath the collectors. More recent amplifiers tend to use a single PNP input pair with resistive loads. Care must be taken to keep the drop across these resistors to much less than a normal diode-drop in order to avoid forward biasing the collector-base junctions when the inputs are at ground.

The question of the output stage is less straightforward. The conventional emitter-follower output stage cannot swing much better than about one Volt to the supply rails, so alternatives have to be found. Some ingenious common-collector output stages have been designed [10],[11] which can usually swing to better than 100 mV, but even this is not close enough for many applications. The only really suitable device for improving this is the MOSFET, and for this reason we have turned to our 36 V CBCMOS process to produce a new generation of single-supply amplifiers. This process features vertical PNP and NPN transistors as well as CMOS devices, and opens up a cornucopia of design possibilities.

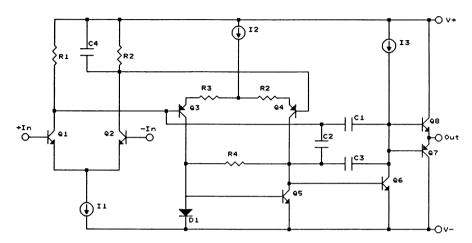

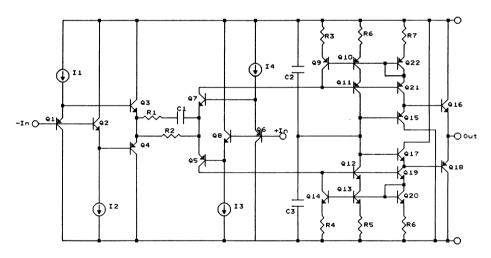

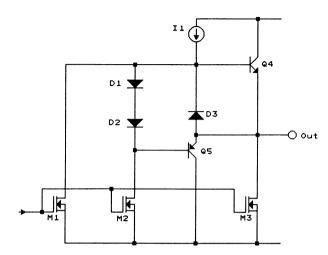

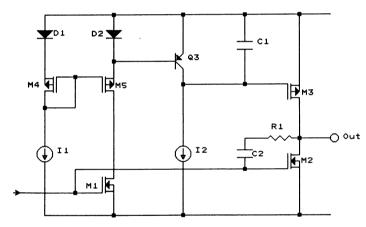

Fig.12 shows an output stage with fairly high speed properties which can operate single or dual supply. When the output is not near the negative rail,  $D_1$  and  $D_2$  bias  $Q_4$  and  $Q_5$  into the conventional class AB mode. As the negative supply is approached,  $M_1$  turns  $Q_4$  completely off and  $M_3$  can pull the output completely to the rail. One drawback of this circuit is that the gain is not very high, and this problem has been alleviated with a new bootstrapped input stage (Fig.13).

$Q_1$  and  $Q_2$  form the input pair and are loaded by  $R_1$ ,  $R_2$  and a foldback cascode consisting of  $Q_3$  and  $Q_4$ . This in turn is loaded by a Wilson current source consisting of  $D_1$ ,  $Q_6$ ,  $Q_7$  and  $Q_8$ . The output impedance of the current source is high, but not high enough to provide precision

performance into a MOSFET type output stage.

Figure 12: Single-supply BiCMOS output stage.

Figure 13: Bootstrapped input stage.

To raise the output impedance, bootstrap transistors  $Q_9$  and  $Q_{10}$  are added. If  $I_2$  is chosen such that the current in  $Q_9$  is equal to the total mirror

current, then the stage theoretically has no  $\beta$ -induced errors, because the base current of  $Q_{10}$  cancels the second-order terms in the Wilson current mirror. A voltage gain in excess of  $10^5$  has been achieved with this input stage.

Some applications require voltage swing to both rails and the output stage of Fig.14 has been developed for this application. The function of  $M_2$  as the pulldown device is fairly obvious but the upper signal path merits some explanation. First note that  $M_5$  is always on and can be initially ignored. This means that the gate drive to  $M_3$  is controlled by  $M_5$  via  $D_2$  and  $Q_3$ . This loop stabilises when the current in  $M_1$  is equal to  $I_2$ , so the quiescent current in  $M_2$  and  $M_3$  is equal to  $I_2$  multiplied by the ratio of  $M_2$  to  $M_1$ . Capacitor  $C_1$  improves stability when driving capacitive loads.

Figure 14: Rail-to rail output stage.

Driving loads in the positive direction,  $M_1$  and  $M_2$  turn off and  $I_2$  applies full gate drive to  $M_3$ . A subtle problem exists when driving in the negative direction, however. In this case, the preceding stage applies full gate drive to  $M_2$ , which enters the linear region.  $M_1$  is still in the saturated region though, and potentially draws a large current under these conditions.  $M_5$  prevents this by limiting the current in  $M_1$  to about five times  $I_2$ , and this in turn means that the output can be driven hard into either rail without incurring excessive supply current.

#### References

- [1] J.R. Ragazzini, R.H. Randall, and F.A. Russell, "Analysis of Problems in Dynamics by Electronic Circuits", *Proc. IRE*, May 1947.

- [2] R.J. Widlar, "I.C. op amp with improved input-current characteristics", *EEE*, December 1968, pp.38-41.

- [3] G. Erdi, "A Low Drift, Low Noise Monolithic Operational Amplifier", Fairchild Semiconductor Application Brief #136, July 1969.

- [4] D. Soderquist and G. Erdi, "The OP-07 Ultra-Low Offset Voltage Op Amp" PMI Application note #13.

- [5] R.J. Widlar, "Design Techniques for Monolithic Operational Amplifiers", *IEEE J. Solid-State Circuits*, vol. SC-4, August 1969, pp.184-191.

- [6] R.J. Apfel and P.R. Gray, "A Monolithic Fast-Settling Feedforward Operational Amplifier using Doublet Compression Techniques", *ISSCC Dig. Tech. Papers*, 1974, pp.134-155.

- [7] J.E. Solomon, "The Monolithic Op Amp: A Tutorial Study", *IEEE J. Solid-State Circuits*, vol. SC-9, December 1974, pp.314-332.

- [8] W.E. Hearn, "Fast slewing monolithic operational amplifier", *IEEE J. Solid-State Circuits*, vol. SC-6, February 1971, pp.20-24.

- [9] D. Bray, "A High Performance Micropower Op-Amp", *Proceedings* of the BCTM, September 1991, pp.281-284.

- [10] R.J. Widlar, "Low Voltage Techniques", *IEEE J. Solid-State Circuits*, December 1978.

- [11] J.H. Huijsing and D. Linebarger, "A low-voltage operational amplifier with rail-to-rail input and output ranges", *IEEE J. Solid-State Circuits*, December 1985.

## **Biography**

Derek F. Bowers is staff vice-president of design at Precision Monolithics Inc., where he has worked for more than 10 years. He has been closely involved in the development of a wide variety of analog devices including op-amps, reference sources, and D/A and A/D converters. Derek Bowers holds a B.Sc. in physics and mathematics from the University of Sheffield, England. In his spare time he enjoys music and brewing.

# Design of Low-voltage Bipolar Opamps

Jeroen Fonderie, J.H. Huijsing

Signetics Company, Sunnyvale, USA

Delft University of Technology, The Netherlands

#### **Abstract**

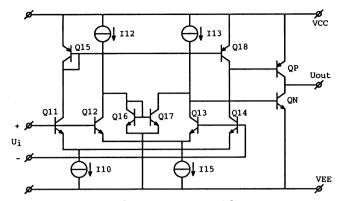

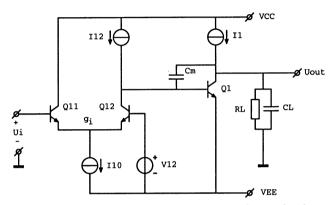

This paper describes design techniques for low-voltage bipolar Operational Amplifiers (OpAmps). The common-mode (CM) input voltage of the OpAmp must be able to have any value that fits within the supply voltage range. An input stage capable of realizing this is discussed. The OpAmp should also have a rail-to-rail output voltage range. The multi-path-driven output stage, which is discussed here has a high bandwidth and a high gain. Miller compensation is used to split the pole frequencies of the OpAmp. Finally, two realizations are discussed and a Figure of merit is defined to enable a comparison of the OpAmps' performances.

#### 1. Introduction

The trend towards very low supply voltages forces new demands on the design of accurate analog building blocks. An important building block is the OpAmp. OpAmps that run on a supply voltage of 1 V have already been in existence for over a decade [1], but until now, the properties of these OpAmps have not allowed accurate signal processing. In this paper techniques to design high-quality low-voltage bipolar OpAmps are highlighted. A more comprehensive discussion can be found in [2].

Why use a low supply voltage? First of all, there is a tendency towards chip components of smaller dimensions. A component with these smaller

dimensions is subject to breakdown at lower voltages. Secondly, battery-powered portable equipment should be able to function at low supply voltages, using just one single battery cell up to the end of its life span. Finally, if low supply voltages are allowed, applying the OpAmp in system design is less critical; the circuit can, for instance, be made to operate from residual voltages within the system.

The question might arise as to whether the OpAmp could preferably be composed of MOS transistors. After all, MOS transistors can potentially be made with a very low threshold voltage. A disadvantage of MOS transistors is, however, that the transconductance of the devices is much smaller than that of bipolar transistors. Furthermore, the minimum drain-source voltage of MOS transistors is usually much larger than the corresponding collector-emitter voltage of a bipolar transistor. This paper is therefore restricted to the use of bipolar transistors.

The design of low-voltage OpAmps is dealt with in the following Sections of the paper. The design of input stages is discussed in Section 2, Section 3 deals with output stages and Section 4 briefly describes the design of intermediate stages. In Section 5 aspects of the high-frequency design of the OpAmp are illustrated and finally, in Section 6, two implementations are presented and a Figure of merit is defined to compare the performance of low-voltage OpAmps.

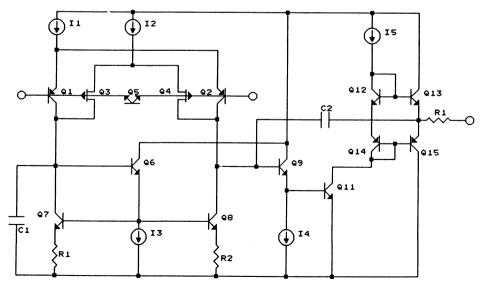

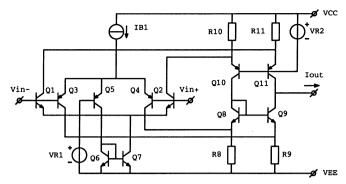

## 2. Input stages

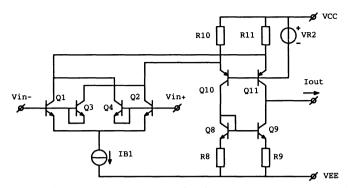

The differential input stage that is shown in Fig.1 has a rail-to-rail CM-input voltage range. In this way a reasonable ratio between the signal and additive interferences, such as noise, is obtained. Further, a rail-to-rail CM-input voltage range also enhances the general-purpose nature of the OpAmp.

If the CM-input voltage is near the negative supply rail, current source  $I_{BI}$  activates the p-n-p pair  $Q_3$ ,  $Q_4$ , provided that the supply voltage is high enough. This p-n-p pair is now able to handle the input signal. If the CM-input voltage is now raised above the reference voltage  $V_{RI}$ , transistor  $Q_5$  takes away the current from current source  $I_{BI}$ , and through  $Q_6$  and  $Q_7$ , supplies the n-p-n pair  $Q_1$ ,  $Q_2$ . The p-n-p pair  $Q_3$ ,  $Q_4$  is now switched off and the signal operation is performed by the n-p-n pair  $Q_1$ ,  $Q_2$ . Even in the turnover range of  $Q_5$ , the sum of the tail currents of the input pairs, and therefore also the total transconductance of the input stage, is kept constant. The value of the reference voltage source  $V_{RI}$  is 0.8 V, high enough to

Figure 1: Input stage with rail-to-rail common-mode input-voltage range and a constant transconductance over the full common-mode range.

Figure 2: The operational regions of the input stage shown in Fig. 1. Only one of the input pairs is active.

enable the n-p-n pair to function properly when the CM-input voltage exceeds this value. The transistors  $Q_{8}$ - $Q_{11}$  and resistors  $R_{8}$ - $R_{11}$  sum the collector currents of the input pairs.

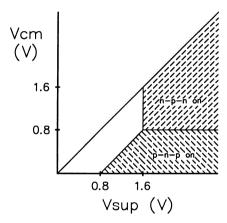

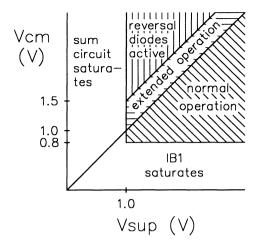

Fig.2 shows the CM range of the input stage as function of the supply voltage, the so-called operational regions. It can be seen that either the p-n-p pair or the n-p-n pair is active, but not both. For supply voltages below 1.6 V (the sum of  $V_{RI}$ , the base-emitter voltage of  $Q_5$  and the saturation voltage of  $I_{BI}$ ) the n-p-n pair is completely shut off and only the p-n-p pair is operative.

Figure 3: Input stage with diodes to prevent reversal of the output signal.

The CM-input voltage range extends beyond the supply rails for approximately 400 mV. This feature is very useful when the OpAmp is used as an inverting amplifier; a small input signal below the negative supply still yields a positive output voltage. However, if the CM-input voltage is increased or decreased still further, the transistors of the input pairs become saturated. This saturation then causes the collector currents of the input-pair transistors to reverse. This reversal is then transferred through the amplifier, leading eventually to reversal of the output signal of the OpAmp. In the circuit shown in Fig.3, this is prevented. For reasons of simplicity, only the n-p-n input pair is shown but the addition to the circuit, which is described below, is valid both for n-p-n as well as for p-n-p input pairs. To prevent the reversal, the diodes  $Q_3$  and  $Q_4$  are inserted. These diodes have twice the size of  $Q_1$ ,  $Q_2$ , and their collectorbase current are therefore also twice as large when saturated. This larger current is used to over-compensate the saturation current of the input-stage transistor by electrically cross-coupling the sensing diodes  $Q_3$ ,  $Q_4$  with the input-pair transistors  $Q_1$ ,  $Q_2$ . Thus the signal polarity remains correct. This results in the ability to overdrive the circuit input to a CM voltage of at least one diode voltage beyond the supply rails.

Fig.4 shows the region of normal operation, the region that extends 400 mV above the supply rail and the region where the reversal diodes are active. If a p-n-p input pair was added to the circuit shown in Fig.3, the area indicated by " $I_{BI}$  saturates" would also be included in the operational regions.

Although not examined here, an input stage with a fully rail-to-rail CM-input range that operates at a minimum supply voltage of 1 V can also be used [3].

Figure 4: Operational regions of the input stage depicted in Fig. 3.

#### 3. Output stages

The output stage of a low-voltage OpAmp should be able to deliver an output voltage signal that is as large as possible, preferably from one supply-voltage rail to the other. After all, the supply-voltage range is by definition not very great, so we want to be able to make full use of it. This rules out the use of emitter followers as output transistors, because such a use would result in the loss of one diode voltage. The actual output transistors of the output stages discussed in this Section therefore have a common-emitter configuration.

The maximum bandwidth of the OpAmp is determined by the current flowing through the output transistors, which determines their transconductance, and by the capacitive load it has to drive. Any transistors preceding the actual CE output transistors more or less reduce the obtainable bandwidth. This reduction should be kept as small as possible.

The output stage should be able to push and pull output currents in the order of 10 mA, which means that its current gain should be in the order of 10<sup>3</sup>. One output transistor in CE configuration does not meet this condition and therefore emitter followers are normally placed in front of it. This contradicts, however, with the previous demand.

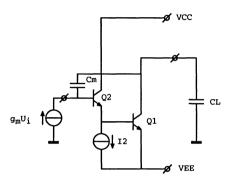

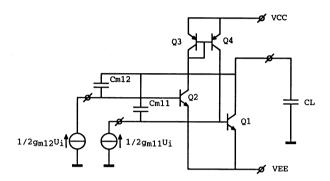

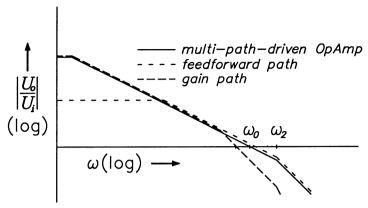

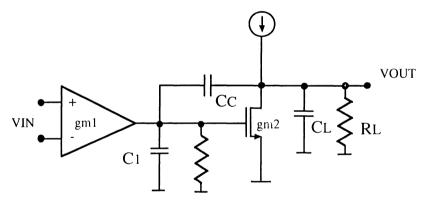

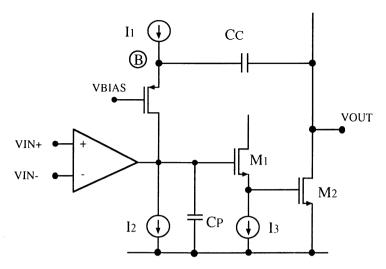

Initially, current-driven output stages with collector outputs have two dominant pole frequencies, one at the input and one at the output. Because the output stage is part of the negative feedback loops within the OpAmp and probably also around it, these two poles will give rise to oscillations. Therefore Miller capacitors are inserted between the input and the output. They split the poles, leaving the output stage with one dominating pole, which yields a stable frequency response [4]. The output stages discussed in this Section are shown with a large capacitive load and no resistive load, because the latter is the most difficult condition where the compensation of the circuits is concerned.

Figure 5: Darlington output stage (n-p-n side).

To illustrate the consequences of the demands stated above, two examples of low-voltage output stages are examined. To increase the current gain of one single CE stage, it can be preceded by an emitter follower. The Darlington output stage that then emerges is shown in Fig.5. Transistors  $Q_1$  and  $Q_2$  are the CE stage and emitter follower, respectively, and the pole splitting is realized with  $C_m$ . Current source  $I_2$  ensures a minimum current through  $Q_2$  at low output currents. The current source  $g_mU_i$  represents the output of the preceding intermediate stage. The minimum supply voltage for this output stage is about 1.7 V.

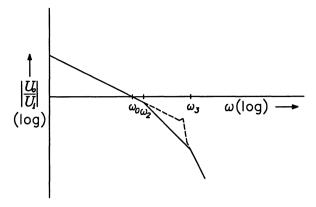

Fig.6 shows the frequency response of the Darlington output stage. Because  $\omega_0$  always has to be chosen smaller than  $\omega_2$  in order to keep a positive phase margin,  $\omega_2$  ultimately sets the bandwidth of the output stage and, consequently, of the complete OpAmp. The position of  $\omega_2$  can be calculated as:

Figure 6: The magnitude of the small-signal voltage gain versus the frequency of the Darlington output stage. The dashed line shows the "output bump" when the output current increases and the poles become complex.

$$\omega_2 = \frac{g_o}{C_L \left(1 + \frac{C_{be2}}{C_m}\right)} \tag{1}$$

where  $g_o$  is the transconductance of the output stage,  $C_L$  is the load capacitor,  $C_m$  is the Miller capacitor and  $C_{be2}$  is the base-emitter capacitance of transistor  $Q_2$ . This leads to the important conclusion that the bandwidth of the OpAmp with a current-driven output stage is determined by the quiescent current through that output stage and by the maximum load capacitor that has to be driven.

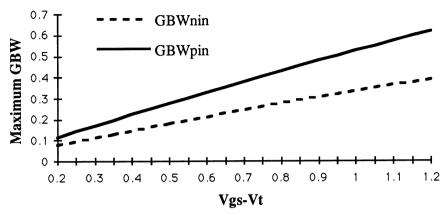

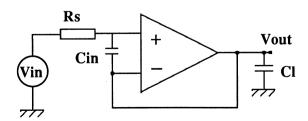

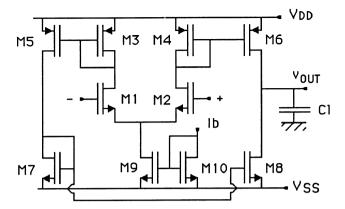

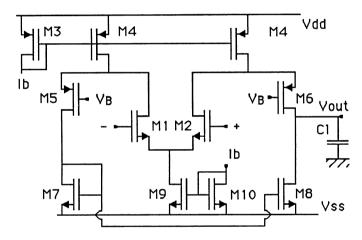

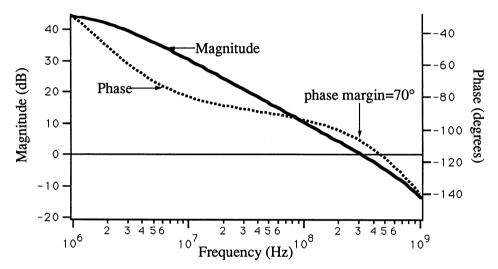

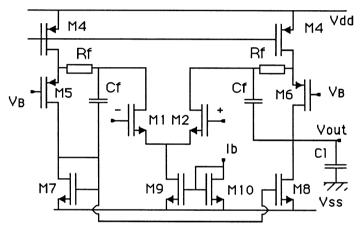

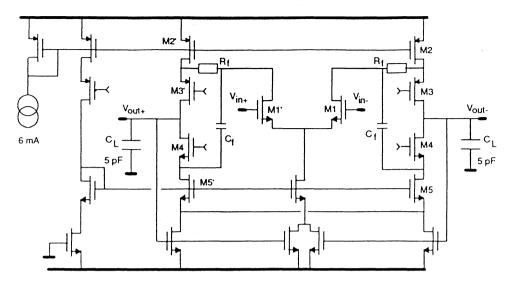

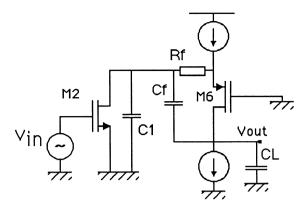

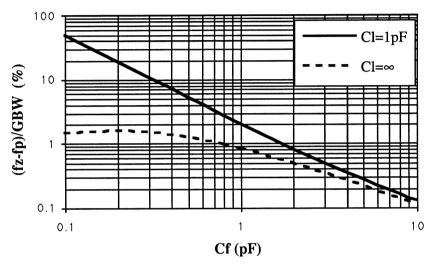

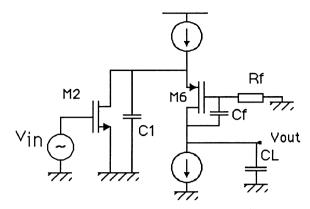

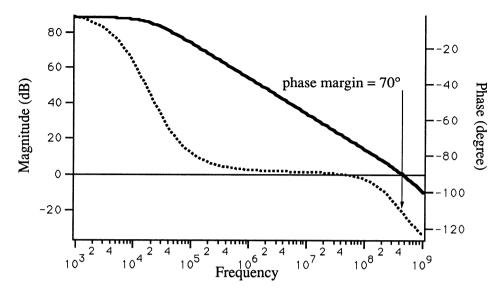

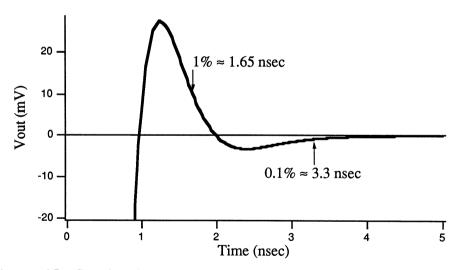

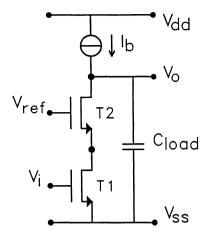

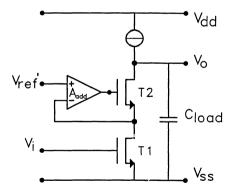

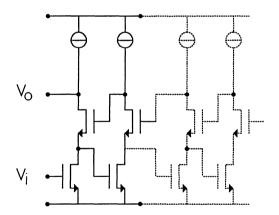

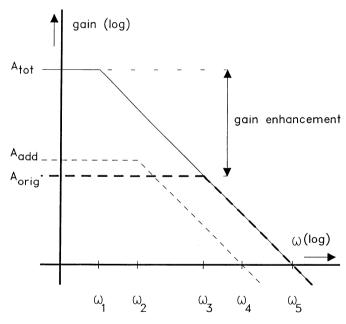

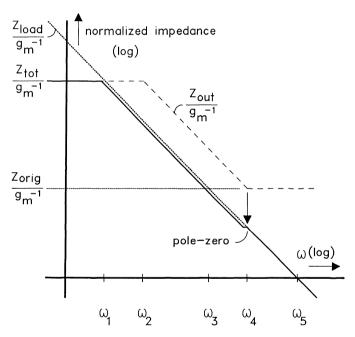

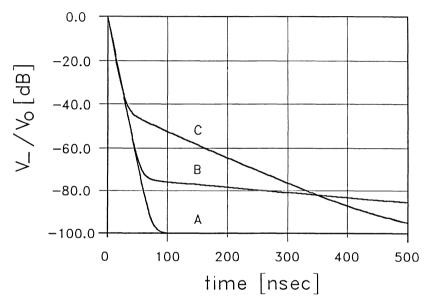

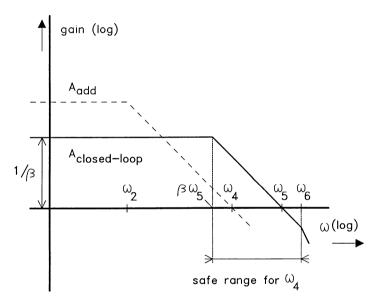

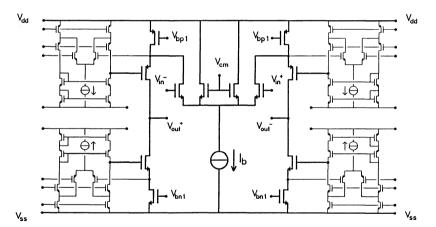

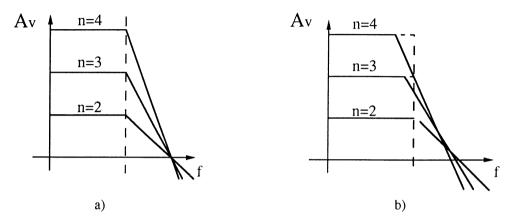

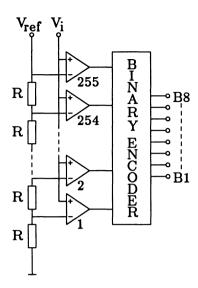

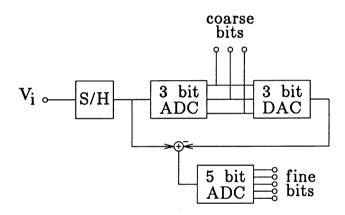

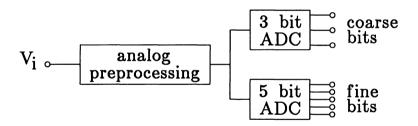

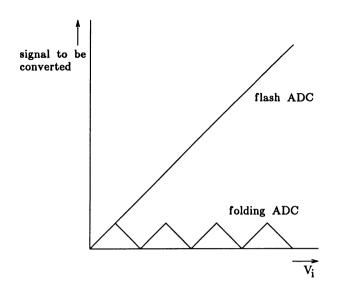

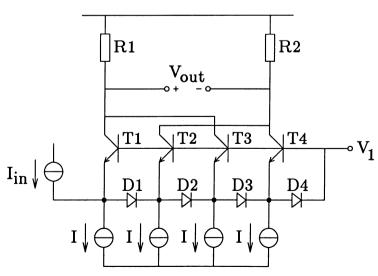

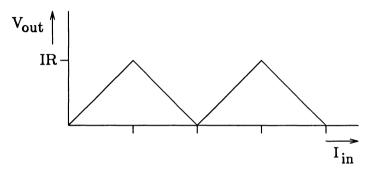

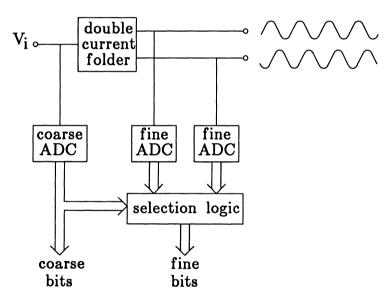

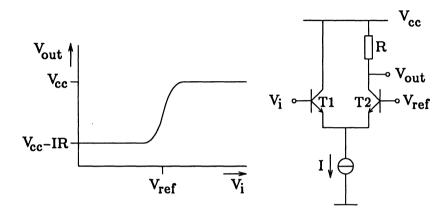

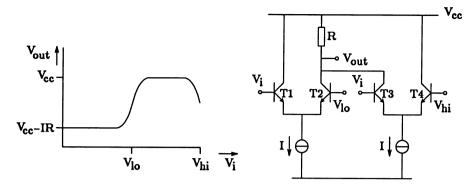

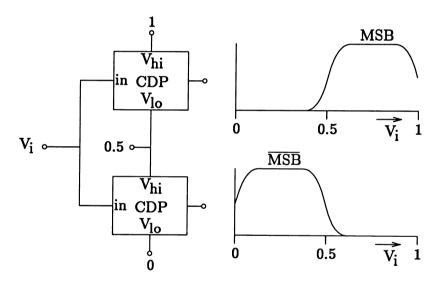

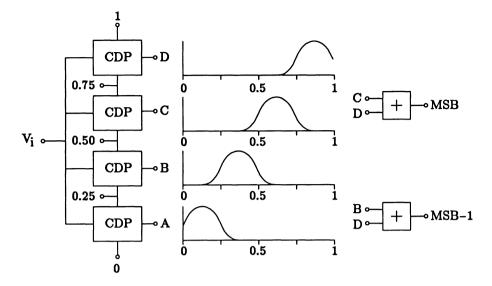

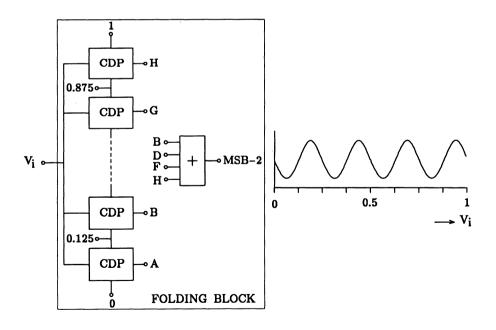

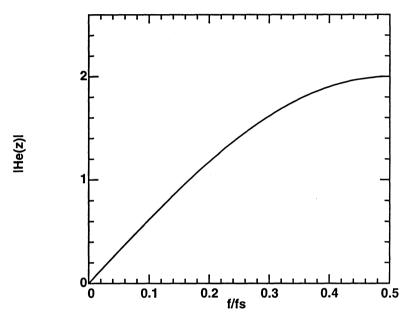

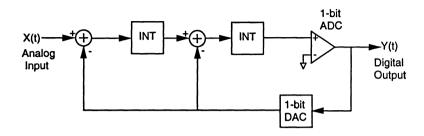

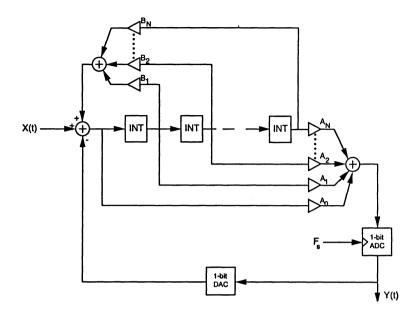

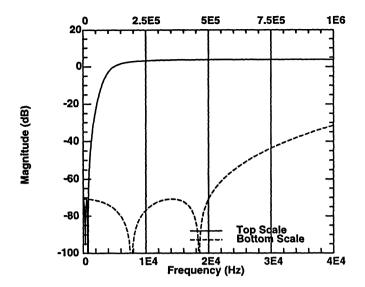

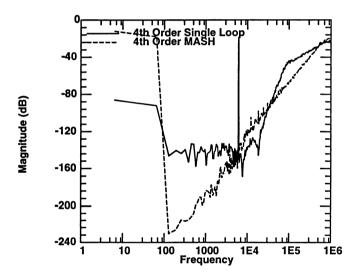

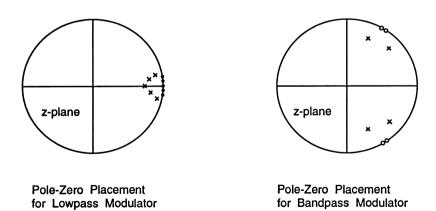

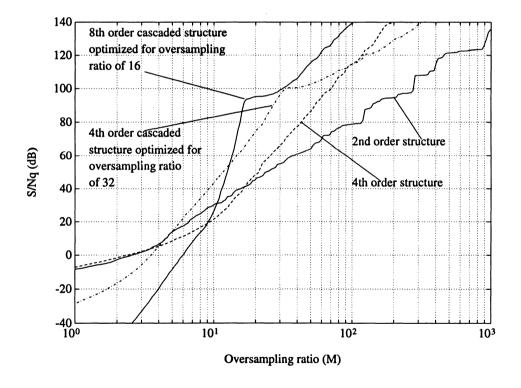

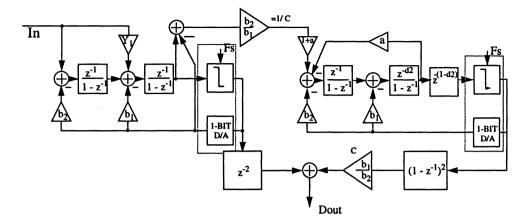

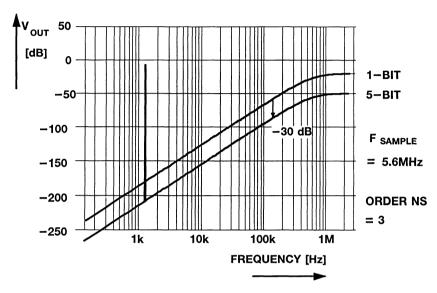

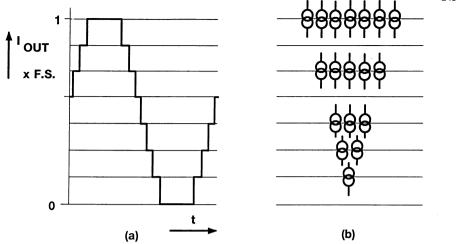

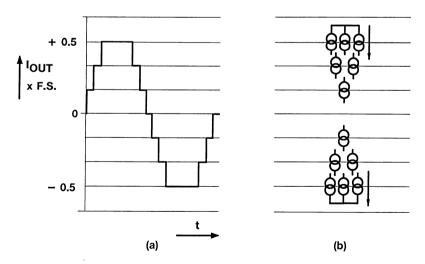

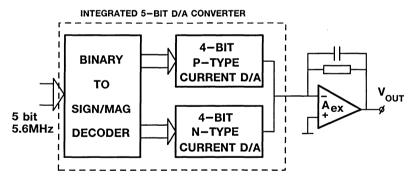

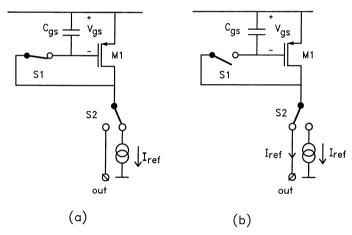

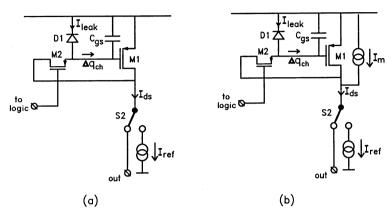

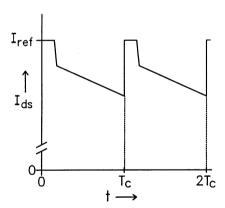

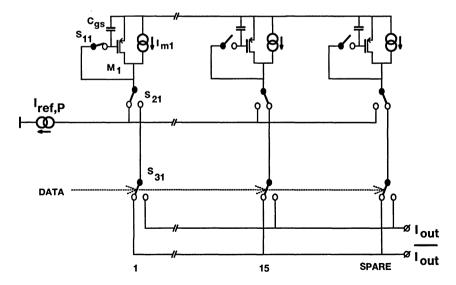

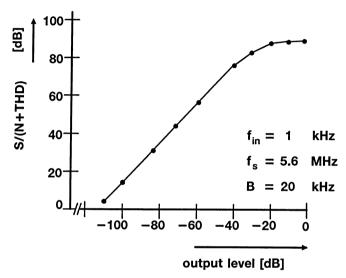

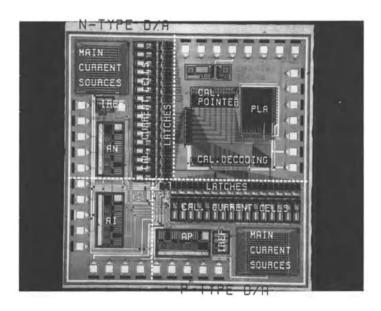

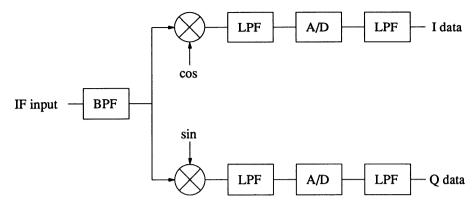

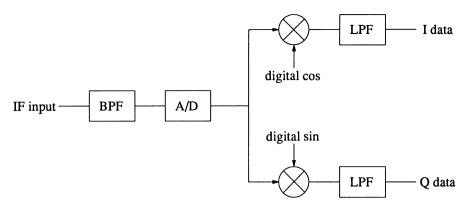

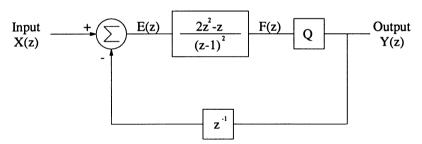

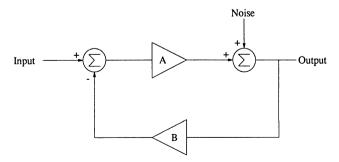

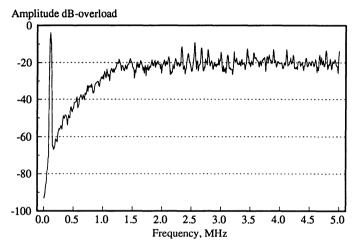

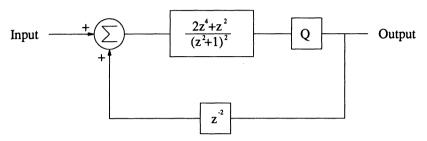

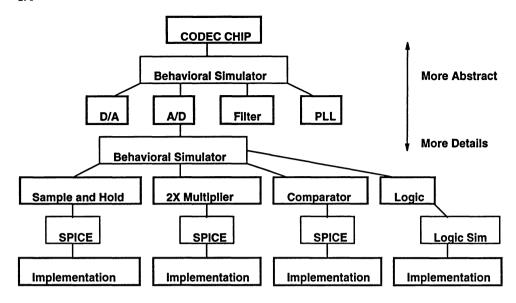

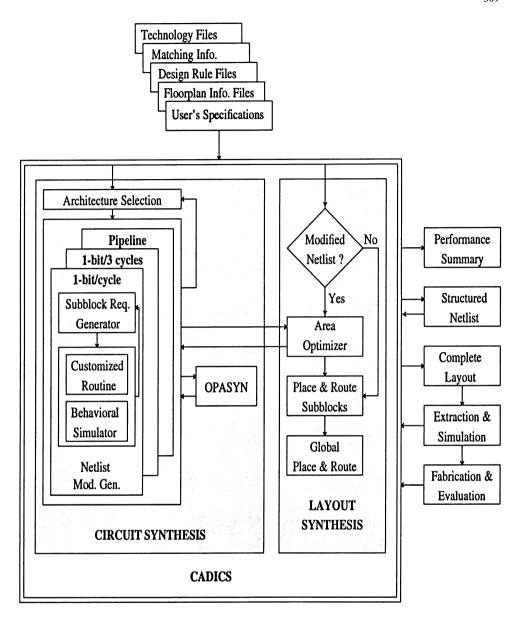

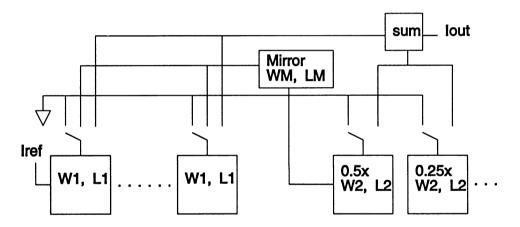

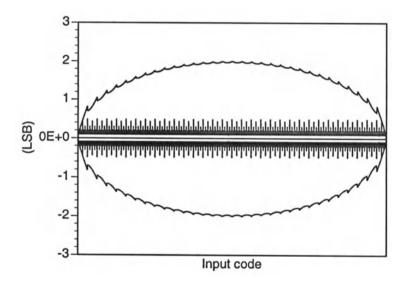

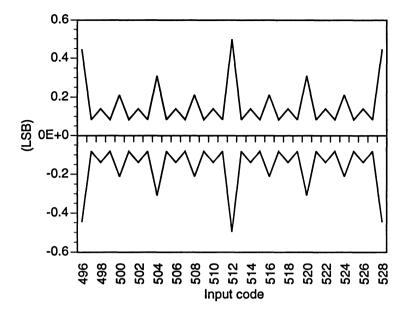

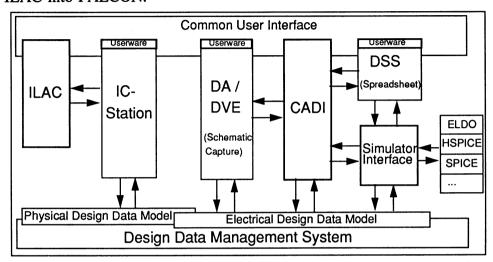

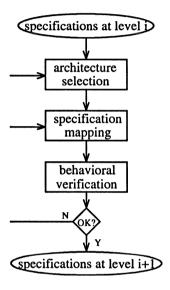

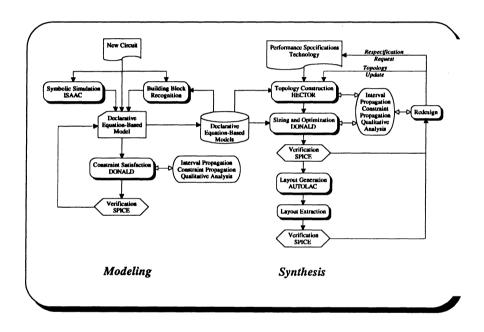

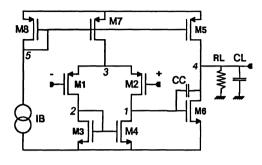

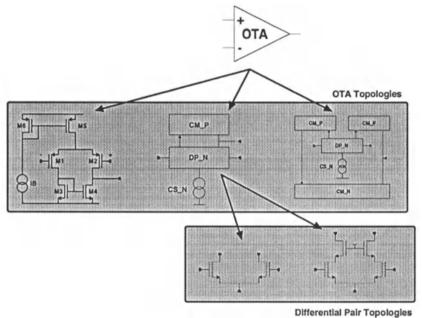

If the output current of the output stage increases,  $\omega_2$  and the high-frequency pole  $\omega_3$ , which is situated at the base of  $Q_1$ , move towards each other and finally collide. The complex poles that then arise cause the famous "output bump" [4], as is shown by the dashed line in Fig.6. These complex poles may have a negative influence on the overall performance of the OpAmp. The presence of complex poles causes damped oscillations in the transient response.